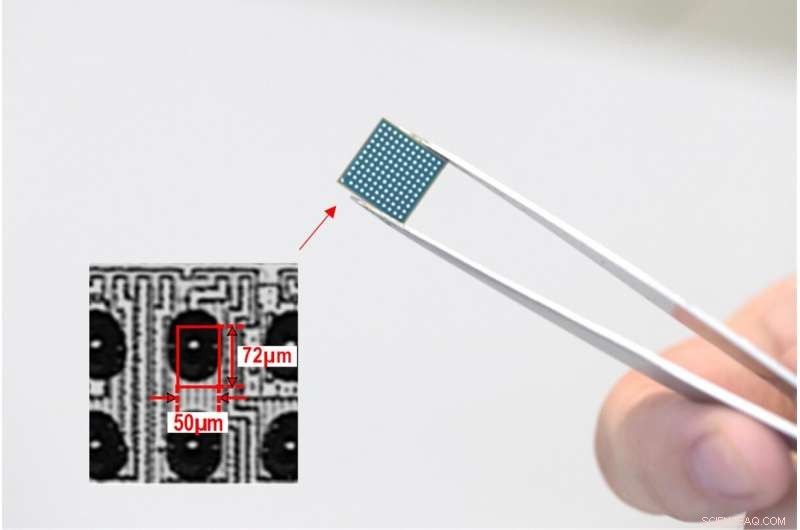

Hela den heldigitala PLL passar i en 50 × 72 μm2 region, vilket gör den till den minsta PLL hittills. Kredit:Kenichi Okada

Forskare vid Tokyo Institute of Technology (Tokyo Tech) och Socionext Inc. har designat världens minsta helt digitala faslåsta loop (PLL). PLL:er är kritiska klockkretsar i praktiskt taget alla digitala applikationer, och att minska deras storlek och förbättra deras prestanda är ett nödvändigt steg för att möjliggöra utvecklingen av nästa generations teknik.

Ny eller förbättrad teknik, som artificiell intelligens, 5G mobilkommunikation, och Internet-of-Things, förväntas medföra revolutionära förändringar i samhället. Men för att det ska hända, högpresterande system-on-a-chip (SoC) – en typ av integrerad krets – enheter är oumbärliga. En central byggsten i SoC-enheter är den faslåsta slingan (PLL), en krets som synkroniserar med frekvensen av en referensoscillation och matar ut en signal med samma eller högre frekvens. PLL genererar klocksignaler, ' vars svängningar fungerar som en metronom som ger en exakt timingreferens för harmonisk drift av digitala enheter.

För att högpresterande SoC-enheter ska kunna realiseras, tillverkningsprocesser för halvledarelektronik måste bli mer sofistikerade. Ju mindre arean för att implementera digitala kretsar är, desto bättre prestanda har enheten. Tillverkare har tävlat om att utveckla allt mindre halvledare. 7 nm halvledare (en massiv förbättring jämfört med deras 10 nm föregångare) är redan i produktion, och metoder för att bygga 5 nm sådana tittar man nu på.

Dock, i denna strävan finns en stor flaskhals. Befintliga PLL:er kräver analoga komponenter, som i allmänhet är skrymmande och har design som är svår att skala ner.

Forskare vid Tokyo Tech och Socionext Inc., ledd av prof. Kenichi Okada, har åtgärdat detta problem genom att implementera en "syntetiserbar" fraktionell-N PLL, som bara kräver digitala logiska grindar, och inga skrymmande analoga komponenter, vilket gör det enkelt att använda i konventionella miniatyriserade integrerade kretsar.

Okada och teamet använde flera tekniker för att minska det nödvändiga området, strömförbrukning och jitter—oönskade tidsfluktuationer vid sändning av digitala signaler—av deras syntetiserbara PLL. För att minska arean, de använde en ringoscillator, en kompakt oscillator som enkelt kan skalas ner. För att dämpa jitter, de minskade fasbruset - slumpmässiga fluktuationer i en signal - för denna ringoscillator, med hjälp av 'injection locking' – processen att synkronisera en oscillator med en extern signal vars frekvens (eller multipel av den) är nära oscillatorns frekvens – över ett brett frekvensområde. Det lägre fasens brus, i tur och ordning, minskad strömförbrukning.

Utformningen av denna syntetiserbara PLL överträffar den hos alla andra aktuella PLL:er i många viktiga aspekter. Den uppnår bästa jitterprestanda med lägsta strömförbrukning och minsta yta (som kan ses i figur 1). "Kärnarean är 0,0036 mm2, och hela PLL är implementerad som en layout med en enda strömförsörjning, " anmärker Okada. Vidare, den kan byggas med standardverktyg för digitala design, möjliggör dess snabba, låg ansträngning, och lågkostnadsproduktion, gör det kommersiellt lönsamt.

Denna syntetiserbara PLL kan enkelt integreras i designen av helt digitala SoCs, och är kommersiellt gångbar, vilket gör det värdefullt för att utveckla den mycket eftertraktade 5 nm halvledaren för banbrytande applikationer inklusive artificiell intelligens, Internet of things och många andra, där hög prestanda och låg strömförbrukning skulle vara de kritiska kraven. Men bidragen från denna forskning går utöver dessa möjligheter. "Vårt arbete visar potentialen hos syntetiserbara kretsar. Med designmetoden som används här, andra byggstenar i SoCs, såsom datakonverterare, strömhanteringskretsar, och trådlösa sändtagare, kan också göras syntetiserbara. Detta skulle avsevärt öka designproduktiviteten och avsevärt minska designansträngningarna, " förklarar Okada. Tokyo Tech och Socionext kommer att fortsätta sitt samarbete i detta för att främja miniatyriseringen av elektroniska enheter, möjliggör förverkligandet av nyare generationens teknologier.