Transistorer i nanoskala är efterfrågade för effektiva digitala kretsar, och förspänning av varje enhet är kritisk. Dessa stringenta förspänningsförhållanden kan mildras genom att erhålla exakta värden på transistorns tröskelspänningar. Detta leder till mer toleranta logiska tillstånd för det elektriska bruset.

För att möta kraven på minskad effektförbrukning, tillverkas CMOS-fälteffekttransistorer (FET) så att de arbetar i förbättringsläge (E), dvs. det finns inga fria laddningsbärare i kanalen vid noll gate-spänning. Å andra sidan har transistorer i utarmningsläge (D) högre strömmar än förbättringsläge på grund av riklig laddningsbärartäthet.

I motsats till växling av FET-applikationer, för högfrekvensapplikationer, är FET-frånläge inte ett obligatoriskt krav. I själva verket är närvaron av en kanal med noll grindförspänning fördelaktig för att erhålla hög transkonduktans vid lägre spänningar. För Si FET:er bestämdes förbättrings- eller utarmningslägena vid tillverkningssteget för jonimplantationsdopning. Det är dock utmanande att implementera denna lösning för den nya generationen tunna material som organiska halvledare och 2D-material.

Enligt ny forskning publicerad i ACS Applied Electronic Materials , genom att välja en speciell arbetsfunktion för en grindmetall, kan tröskelspänningarna för FET:erna av p-typ ändras från negativa till positiva värden, vilket är selektiv växling mellan förbättringsläge och utarmningsläge.

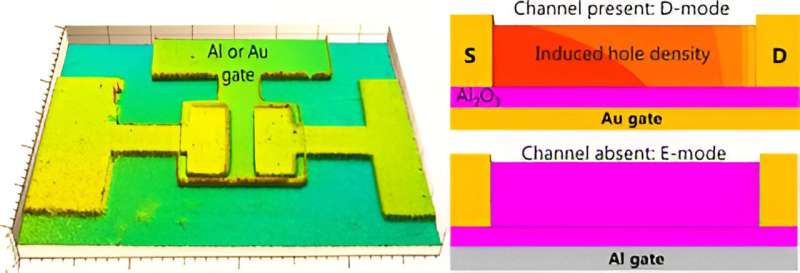

Forskarna tillverkade experimentellt FET:erna med olika gatemetallelektroder med olika arbetsfunktioner. Den dielektriska aluminiumoxidtjockleken var bara 5 nm. På grund av denna korta separation mellan gatemetallen och den organiska halvledande kanalen av p-typ, fanns det elektrostatisk interaktion mellan dem även utan applicering av extern spänning. När metall med låg arbetsfunktion som aluminium (4,4 eV) används, fungerar FET i förbättringsläge.

För gatemetaller med hög arbetsfunktion som guld (5,0 eV) induceras ett visst antal hål i kanalen vid noll gate-spänning. Detta leder till en bra mängd ström, vilket är känt som utarmningsläge.

För att bekräfta denna experimentella observation utförde forskarna TCAD-enhetssimuleringar. Simuleringarna producerade färgkonturdiagram av inducerad håldensitet. Den här typen av matchande experiment- och simuleringsresultat är mycket viktiga ur teknisk synvinkel och storskalig produktion.

Huvudförfattaren, Dr. Abhay Sagade från SRMIST, Indien, avslöjade att de observerade effekterna är djupgående för tunna dielektriska tjocklekar som de mindre än 10 nm. För större tjocklekar förblir FET:erna i förbättringsläge även för gatemetaller med hög arbetsfunktion.

Detta koncept kan enkelt utökas till alla tunna organiska, oorganiska och nya generationens 2D-material. Med denna metod borde det vara möjligt att tillverka mer kompakta, exakta och omkonfigurerbara digitala logik- och oscillatorenheter och kretsar. Vidare kan D-mode OFETs med förbättrade strömmar användas effektivt för högfrekventa tillämpningar.

Detta har också enorma konsekvenser för kommande kvantenheter och tekniska applikationer som använder smådimensionellt känsliga enheter.

Mer information: Abhay A. Sagade, Selective Operation of Enhancement and Depletion Modes of Nanoscale Field-Effect Transistors, ACS Applied Electronic Materials (2024). DOI:10.1021/acsaelm.3c01825

Tillhandahålls av SRM Institute of Science and Technology