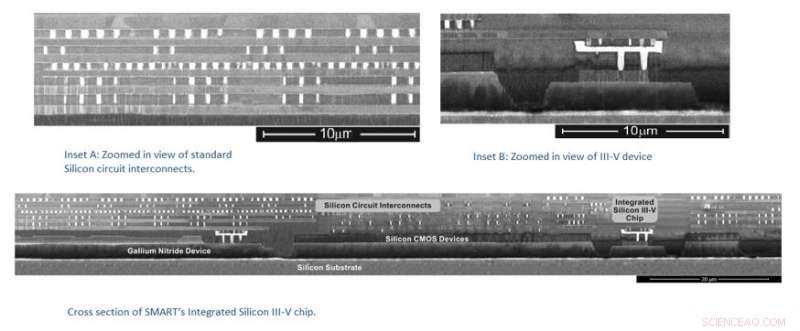

Tvärsnitt av SMARTs Integrated Silicon III-V-chip. Kredit:SMART

Singapore-MIT Alliance for Research and Technology (SMART), MIT:s forskningsföretag i Singapore, har tillkännagivit framgångsrik utveckling av ett kommersiellt gångbart sätt att tillverka integrerade Silicon III-V-chips med högpresterande III-V-enheter infogade i deras design.

I de flesta enheter idag, kiselbaserade CMOS-chips används för datoranvändning, men de är inte effektiva för belysning och kommunikation, vilket resulterar i låg verkningsgrad och värmealstring. Det är därför de nuvarande 5G-mobilenheterna på marknaden blir väldigt heta vid användning och skulle stängas av efter en kort tid.

Det är här III-V-halvledare är värdefulla. III-V-chips är gjorda av grundämnen i den tredje och femte kolumnen i det elementära periodiska systemet, såsom Gallium Nitride (GaN) och Indium Gallium Arsenide (InGaAs). På grund av deras unika egenskaper, de är exceptionellt väl lämpade för optoelektronik (LED) och kommunikation (5G etc) - vilket ökar effektiviteten avsevärt.

"Genom att integrera III-V i kisel, vi kan bygga vidare på befintliga tillverkningsmöjligheter och lågkostnadstekniker för volymproduktion av kisel och inkluderar den unika optiska och elektroniska funktionaliteten hos III-V-teknik, sa Eugene Fitzgerald, VD och direktör, SMART, MIT:s forskningsföretag i Singapore. "De nya chipsen kommer att utgöra hjärtat av framtida produktinnovation och driva nästa generations kommunikationsenheter, wearables och displayer."

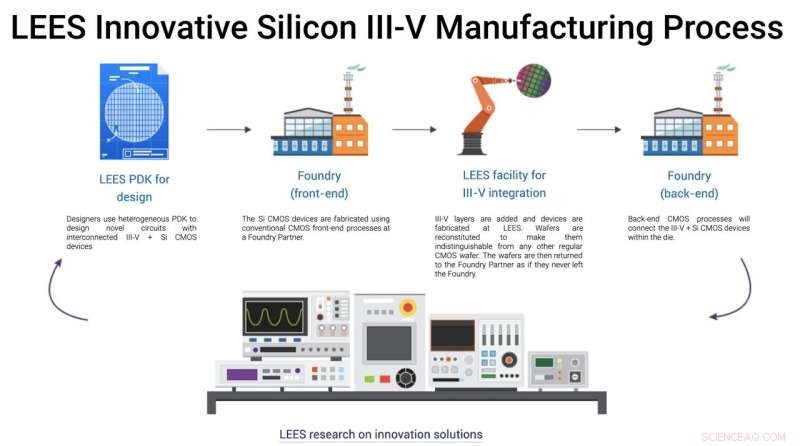

LEES-forskare granskar en 200 mm Silicon III-V wafer. Den innovativa och kommersiellt redo processen av LEES utnyttjar befintlig 200 mm halvledartillverkningsinfrastruktur för att skapa en ny generation chips som kombinerar traditionell Silicon med III-V-enheter, något som inte var kommersiellt gångbart innan Kredit:SMART

Kenneth Lee, Senior vetenskaplig chef för forskningsprogrammet SMART LEES tillägger:"Men Att integrera III-V-halvledarenheter med kisel på ett kommersiellt gångbart sätt är en av de svåraste utmaningarna för halvledarindustrin, även om sådana integrerade kretsar har varit önskvärda i årtionden. Nuvarande metoder är dyra och ineffektiva, vilket försenar tillgången på de chips som industrin behöver. Med vår nya process, vi kan utnyttja befintliga möjligheter för att tillverka dessa nya integrerade Silicon III-V-chips kostnadseffektivt och påskynda utvecklingen och införandet av ny teknik som kommer att driva ekonomier."

Den nya tekniken som utvecklats av SMART bygger två lager av kisel- och III-V-enheter på separata substrat och integrerar dem vertikalt tillsammans inom en mikron, vilket är 1/50 av diametern på ett människohår. Processen kan använda befintliga 200 mm tillverkningsverktyg, vilket kommer att göra det möjligt för halvledartillverkare i Singapore och runt om i världen att nyttja sin nuvarande utrustning. I dag, kostnaden för att investera i en ny tillverkningsteknik är i intervallet tiotals miljarder dollar, sålunda är denna nya integrerade kretsplattform mycket kostnadseffektiv och kommer att resultera i mycket billigare nya kretsar och elektroniska system.

SMART fokuserar på att skapa nya marker för pixelerad belysning/display och 5G -marknader, som har en kombinerad potentiell marknad på över $ 100B USD. Andra marknader som SMARTs nya integrerade Silicon III-V-chip kommer att störa inkluderar bärbara miniskärmar, virtual reality -applikationer, och andra bildtekniker.

Hur LEES tillför värde till din produktion. Kredit:SMART

Patentportföljen har exklusivt licensierats av New Silicon Corporation Pte. Ltd. (NSC), en Singapore-baserad spin-off från SMART. NSC är det första fabellösa integrerade kretsföretaget i kisel med proprietära material, processer, enheter, och design för monolitiska integrerade Silicon III-V-kretsar (www.new-silicon.com).

SMARTs nya integrerade Silicon III-V-chip kommer att finnas tillgängliga nästa år och förväntas i produkter 2021.