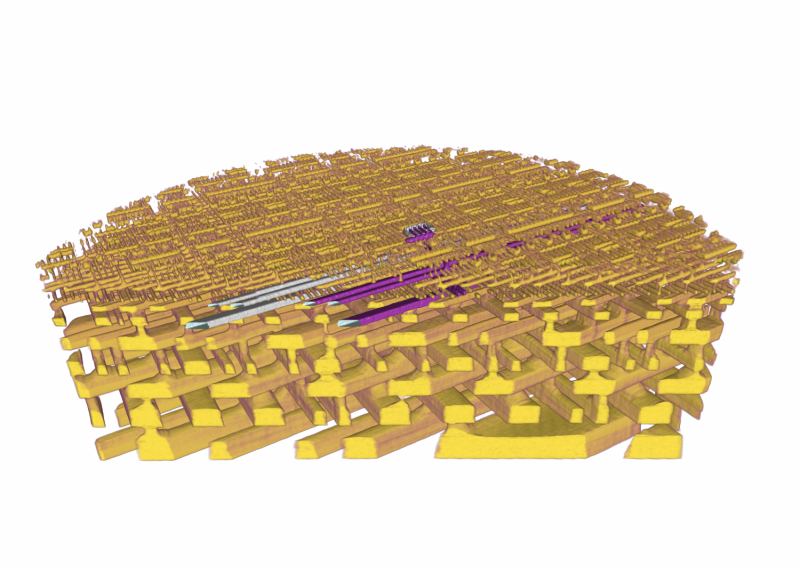

3D-representation av den interna strukturen hos ett mikrochip (en Intel-processor). Vyn som visas är exakt på den nivå där transistorerna är. Materialet i gult är koppar - visar processorns kretsanslutningar som länkar de enskilda transistorerna med varandra. För att illustrera, flera sammankopplingar vars linjer kunde följas genom den undersökta volymen har färgats. Linjerna som visas individuellt är cirka 45 nanometer breda (45 miljoner miljondelar); i alla, en bit av processorn på cirka 10 mikrometer (10 tusendels millimeter) i diameter undersöktes. Kredit:Paul Scherrer Institute/Mirko Holler

Forskare vid Paul Scherrer Institute PSI har gjort detaljerade 3D-bilder av ett kommersiellt tillgängligt datorchip. Detta är första gången en icke-destruktiv metod har visualiserat banorna för ett chips interna ledningar (bara 45 nanometer-45 miljoner millimeter-bred) och dess 34-nanometer höga transistorer tydligt utan snedvridningar eller deformationer. Det är en stor utmaning för tillverkarna att avgöra om, i slutet, deras chips överensstämmer med specifikationerna. Således representerar dessa resultat en viktig tillämpning av en röntgentomografimetod som PSI-forskarna har utvecklat i flera år. I deras experiment, forskarna undersökte en liten bit som de hade skurit ut ur chipet i förväg. Detta prov förblev oskadat under hela mätningen. Målet är nu att förlänga metoden på ett sådant sätt att den kan användas för att undersöka kompletta marker. Forskarna genomförde experimenten vid Swiss Light Source SLS från Paul Scherrer Institute.

De rapporterar sina resultat i den senaste upplagan av tidskriften Natur .

De elektriska ledningarna i många av de elektroniska chipsen i våra datorer och mobiltelefoner är bara 45 nanometer breda, transistorerna 34 nanometer höga. Även om det är standard praxis idag att producera strukturer som är så känsliga, det är fortfarande en utmaning att mäta den exakta strukturen hos ett färdigt chip i detalj för att kontrollera, till exempel, om den är byggd enligt specifikationerna. Nu för tiden, för sådana undersökningar, tillverkare använder huvudsakligen en metod där lager efter lager av chipet tas bort och sedan, efter varje steg, ytan undersöks med ett elektronmikroskop; detta är känt som FIB/SEM—fokuserad jonstråle/svepelektronmikroskopavbildning.

Nu har forskare vid Paul Scherrer Institute PSI använt röntgenstrålar för att uppnå oförstörande 3D-avbildning av ett chip, så att banorna för de ledande ledningarna och positionerna för de enskilda transistorerna och andra kretselement blev tydligt synliga. Bildupplösningen vi kunde producera är jämförbar med den konventionella FIB/SEM -undersökningsmetoden, förklarar Mirko Holler, projektledare. Men vi kunde undvika två betydande nackdelar:För det första, provet förblev oskadat, och vi har fullständig information om den tredimensionella strukturen. För det andra, vi undvek snedvridningar av bilderna som uppstår i FIB/SEM om ytan på det enskilda segmentet inte är exakt plan.

Placerad med nanometerprecision

För sina studier, forskarna använde en speciell tomografisk metod (ptychotomography) som de har utvecklat och förbättrat under de senaste åren, och som idag erbjuder världens bästa upplösning på 15 nanometer (15 miljoner miljondelar) för undersökning av en jämförelsevis stor volym. I experimentet röntgas objektet som ska studeras på exakt bestämda platser med ljus från den schweiziska ljuskällan SLS från Paul Scherrer-institutet-för varje upplyst plats mäter en detektor sedan röntgenmönstret efter dess passage genom provet . Provet roteras sedan i små steg och röntgas sedan igen stegvis efter varje varv. Från hela uppsättningen data som erhållits, provets tredimensionella struktur kan bestämmas. Med dessa mätningar, provets position måste vara känd med en precision på bara några nanometer - det var en av de särskilda utmaningarna för att sätta upp vår experimentstation, säger Holler.

I sitt experiment undersökte forskarna små bitar av två chips - ett detektorchip som utvecklats vid PSI och ett kommersiellt tillgängligt datorchip. Varje bit var cirka 10 mikrometer (det vill säga 10 tusendels millimeter) i storlek. Även om det inte är möjligt att undersöka ett helt chip med den nuvarande mätinställningen, metodens fördelar uppnås även i denna form, så att de första potentiella användarna redan har uttryckt intresse för att utföra mätningar på PSI.

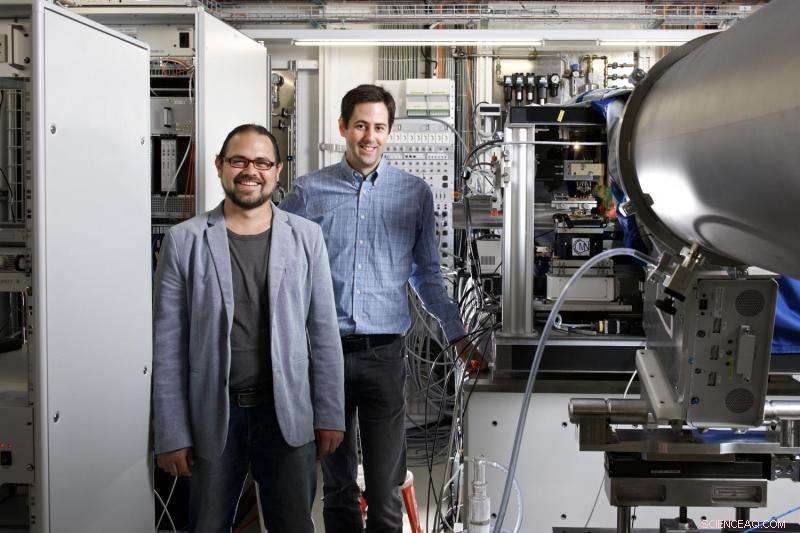

PSI-forskarna Mirko Holler (höger) och Manuel Guizar-Sicairos vid cSAXS-strållinjen för den schweiziska ljuskällan SLS vid Paul Scherrer-institutet. Här gjorde de den tredimensionella strukturen av ett mikrochip synligt. Upphovsman:Paul Scherrer Institute/Markus Fischer

Målet:att undersöka hela mikrochips

Vi börjar för närvarande att förlänga metoden på ett sådant sätt att den kan användas för att undersöka hela mikrochips inom en acceptabel mättid. Då blir det också möjligt att studera samma område av ett chip flera gånger, till exempel för att observera hur det förändras under yttre påverkan, förklarar Gabriel Aeppli, chef för Synchrotron Radiation and Nanotechnology Division vid PSI.

En andra 3D-representation av den inre strukturen i ett mikrochip (en Intel-processor). Kredit:Paul Scherrer Institute/Mirko Holler