I hjärtat av den avancerade halvledarchipteknologin ligger en kritisk utmaning:att skapa mindre, mer effektiva elektroniska komponenter. Denna utmaning är särskilt uppenbar inom området litografi, den process som används för att skapa intrikata mönster på halvledarmaterial (kallade wafers) för produktion av chips.

Litografi använder en sorts mall, som kallas en fotomask - eller bara mask - för att skapa mönster på halvledarskivor. Industrin letar alltid efter metoder som förbättrar upplösning och tillverkningsbarhet för både masker och wafers, vilket kommer att producera snabbare chips med högre utbyte av väl fungerande chips.

Beräkningslitografitekniker som förbättrar upplösning och mönstertrohet, såsom optisk närhetskorrigering (OPC), har gjort betydande framsteg för att ta itu med dessa utmaningar genom att modifiera de individuella maskmönstren för att förbättra både mask- och waferutskrift.

Invers litografiteknik (ILT) – ett matematiskt rigoröst omvänt tillvägagångssätt som bestämmer maskformerna som ger önskade resultat på wafern – har setts som en lovande lösning på många av utmaningarna med litografi för avancerade chips. Sedan introduktionen för mer än ett decennium sedan har det gjorts många studier som visar att i synnerhet kurvlinjära ILT-maskformer ger de bästa waferresultaten.

Tills nyligen har dock körtiderna som är förknippade med denna beräkningsteknik begränsat dess praktiska tillämpning till kritiska "hotspots" på chips. Under 2019 föreslogs ett helt nytt, specialbyggt system, inklusive ett unikt GPU-accelererat tillvägagångssätt som emulerar ett enda, gigantiskt GPU/CPU-par som kan beräkna en hel ILT-lösning med full chip på en gång. Detta nya tillvägagångssätt, systematiskt utformat för ILT- och GPU-acceleration, gjorde full-chip ILT till en praktisk verklighet i produktionen.

Detta tillvägagångssätt förlitade sig dock på maskskrivning med flera strålar, en viktig nyutveckling inom maskskrivning som är pixelbaserad och likaså formagnostisk när det gäller skrivtid. Frågan som återstod var om fördelarna med full-chip, krökt ILT kunde utvidgas till maskskrivare med variabel form (VSB) som skriver rätlinjiga (och ibland triangel) former snarare än pixlar, och som utgör majoriteten av maskritare runt om i världen idag.

Medan VSB-skrivare snabbt skapar större rektangulära former genom att skriva en rektangulär bild åt gången, kan komplexa maskmönster vara ett problem eftersom det stora antalet små rektanglar som behövs för att skapa dem skulle ta för lång tid att skriva.

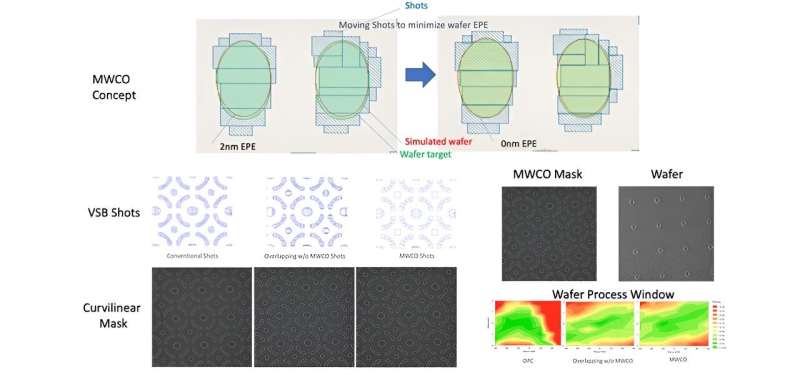

Rapporterar deras arbete i Journal of Micro/Nanopatterning, Materials, and Metrology , uppfann teamet vid D2S, Inc. en metod som kallas mask wafer co-optimization (MWCO) med tre insikter:maskskrivaren och waferskannern är båda lågpassfilter; överlappande skott styrda av mask/wafer-simulering kan skapa kurvlinjära former med färre skott; genom att rikta in sig på wafermönstret, istället för maskmönstret, kan man skapa mycket enklare bilder för att skriva ut rätt wafermönster. Genom att använda denna dubbla simulering optimeras wafer-utskriftskvaliteten iterativt samtidigt som VSB-skottkanter manipuleras för att producera rätlinjiga målmaskformer som är kända för att vara skrivbara på en VSB-skrivare, med ett känt och acceptabelt antal skott.

D2S och Micron Technology har visat att MWCO kan minska wafervariationen med 3x och kan förbättra waferprocessfönstret med 2x jämfört med Micron OPC, vilket indikerar en avsevärd förbättring av precisionen och tillförlitligheten i litografiprocessen. Skrivtiden för en hel krökt ILT-mask skulle vara mindre än 12 timmar, vilket tillfredsställer produktionskraven för stora volymer.

Detta innebär att alla halvledartillverkare nu kan producera chip som inte bara är mindre utan också har högre prestanda och lägre strömförbrukning, även om de inte har tillgång till en multi-beam maskritare.

Mer information: Linyong (Leo) Pang et al, Gör det omöjliga möjligt:använd maskskrivare med variabel form och krökt helchips invers litografiteknik för 193i-kontakter/vias med mask-wafer-samoptimering, Journal of Micro/Nanopatterning, Material och metrologi (2024). DOI:10.1117/1.JMM.23.1.011207

Tillhandahålls av SPIE