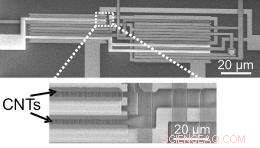

En elektronmikroskopbild som visar kolnanorörstransistorer (CNT) arrangerade i en integrerad logisk krets.

(PhysOrg.com) -- Stanfords ingenjörer har byggt vad de tror är ett chip med de mest avancerade beräknings- och lagringselementen gjorda av kolnanorör hittills genom att utarbeta ett sätt att utrota den envisa komplikationen av nanorör som orsakar kortslutningar.

Nanorör, som liknar mikroskopiska sugrör av ihoprullad kycklingnät, ses allmänt som den potentiella nästa generationens material för att möjliggöra förbättrad hastighet och energieffektivitet för datorchips.

Forskarna presenterade sina resultat idag vid International Electron Devices Meeting (IEDM) i Baltimore, tillsammans med ytterligare ett framsteg i att använda nanorör för att göra flerskiktade, tredimensionella kretsar.

"Detta arbete illustrerar att kolnanorörstransistorteknologi har rört sig bortom sfären av vetenskapliga upptäckter och in i teknisk forskning, " sa H.-S. Philip Wong, professor i elektroteknik vid Stanford och medförfattare till uppsatsen. "Vi kan nu konstruera enheter och bygga kretsar i en wafer-skala i motsats till tidigare demonstrationer av "one-of-a-kind". Enheter är i en kretsmiljö som är relevant för både dagens och morgondagens systembehov."

Den handfull nanorörstransistorer i kretsarna som laget tillverkade kan inte jämföras med hundratals miljoner transistorer på en kommersiell mikroprocessor eller minneschip, men deras arrangemang, hur de tillverkades och deras egenskaper är mycket närmare kommersiell kvalitet än någon nanorörsenhet som tillverkats tidigare, sa Subhasish Mitra, en biträdande professor i datavetenskap och elektroteknik vid Stanford.

Transistorerna är grupperade i samma "kaskadande" sekvenser som behövs för att producera beräkningslogik och minne, och processen som används för att tillverka dem är kompatibel med tillverkningsstandarden för industriell VLSI (mycket storskalig integration).

"Vi är mycket nöjda med de snabba framstegen som görs av professorerna Wong och Mitra och deras forskarteam i att utveckla dessa teknologier för att hjälpa till att övervinna hinder för ytterligare integration av komplexa kolbaserade elektroniska kretsar, som kommer att leda till mer användbara produkter för framtida generationer, sa Betsy Weitzman, vice vd och direktör för Semiconductor Research Corporations Focus Center Research Program, som hjälpte till att finansiera forskningen, tillsammans med National Science Foundation.

Chipsen använder tre avancerade tekniker som uppfanns vid Stanford för att övervinna endemiska problem i samband med nanorör. Ett, uppfanns 2007, tillåter transistorer att fungera oavsett om komponentnanorören ligger helt rakt. Annan, uppfanns 2008, möjliggör VLSI-skala tillverkning av nanorörstransistorer på ett chip. Den som tillkännagavs idag på IEDM, är en process för att på ett tillförlitligt sätt ta bort nanorör som alltid leder elektrisk ström även när de inte är tänkta. Sådana besvärliga "metalliska" nanorör kan kortsluta transistorer om de inte tas bort. Svårigheten forskare har ställts inför är att hitta sätt att ta bort alla besvärliga nanorör, utan att skada någon annan del av en krets, inklusive nanorör som beter sig korrekt.

Den nya tekniken, som forskarna kallar VLSI-kompatibel metallisk nanotubborttagning (VMR), bygger på en idé som först föreslogs av Paul Collins och kollegor på IBM 2001. Tanken var att bryta upp nanorören genom att utsätta dem för stark ström. Stanford-teamet har nu gjort idén praktisk i VLSI-skala genom att skapa ett rutnät av elektroder som zappar bort de oönskade nanorören. Samma elektrodnät kan sedan etsas för att producera vilken kretsdesign som helst, inklusive de som använder sig av Stanford-utvecklade tekniker som nämns ovan.

Huvudförfattaren på VMR-uppsatsen som presenterades vid IEDM är elteknik Stanford-studenten Nishant Patil. Andra författare inkluderar elektroteknikstudenter Albert Lin, Jie Zhang och Hai Wei, och student Kyle Anderson.

3-D nanorörskretsar

Fem medlemmar i teamet (Wei, Patil, Lin, Wong och Mitra) följde omedelbart upp VMR-uppsatsen vid IEDM med en annan presentation som beskrev den första tredimensionellt integrerade kretsen av kolnanorör i flera lager.

Som parkeringshus i flera nivåer, tredimensionella kretsar möjliggör packning av fler enheter - i detta fall, transistorer - in i ett begränsat område. På chips, den tredje dimensionen kan också minska längden på vissa sammankopplande ledningar, minska energi som krävs för dataöverföring. Medan ingenjörer nyligen har börjat göra framsteg i att bygga tredimensionella kretsar genom att stapla och koppla samman lager gjorda med konventionella material, Stanford-arbetet visar att det kan göras med nanorör på ett sätt som är integrerat från början som en 3D-design, ger en högre täthet av anslutningar mellan skikt.

Indikerar att framsteg kan vara möjliga med nanorör, Stanford-forskarna kunde skapa en prototyp av trelagerschip med dussintals nanorörstransistorer som var anslutna i fungerande logiska grindar med nanorörs- och metallledningar. Vad gjorde bedriften möjlig, Mitra sa, var användningen av en relativt låg temperaturprocess som forskarna utvecklade förra året där nanorör överförs från en kvartswafer till ett kiselchip.

En återstående utmaning är att öka antalet nanorör som kan mönstras på rätt sätt på ett visst område av ett chip, för att möjliggöra tillverkning av de miljontals transistorer som modern design kräver. Det är inte ett hinder som forskare förväntar sig att lämna obehindrat.

Båda projekten stöddes av Focus Center Research Program och National Science Foundations Directorate for Computer and Information Science and Engineering (CISE).

"NSF och i synnerhet CISE, är mycket intresserad av att utforska spännande nya vägar för att erhålla fortsatta förbättringar av hårdvaruprestanda bortom gränserna för Moores lag, " sa Sampath Kannan, en divisionsdirektör för CISE vid National Science Foundation.

"Teamet ledd av professorerna Mitra och Wong, stöds av flera anslag från CISE, är banbrytande forskning längs en av dessa vägar. Deras nya resultat på teknik i VLSI-skala för att hantera metalliska kolnanorör för kretsdesign och deras experimentella demonstration av imperfektionsimmuna VLSI-kompatibla CNT-kretsar tar oss närmare att göra integrerade kretsar med kolnanorör till en praktisk verklighet."

Tillhandahålls av Stanford University (nyheter:webb)