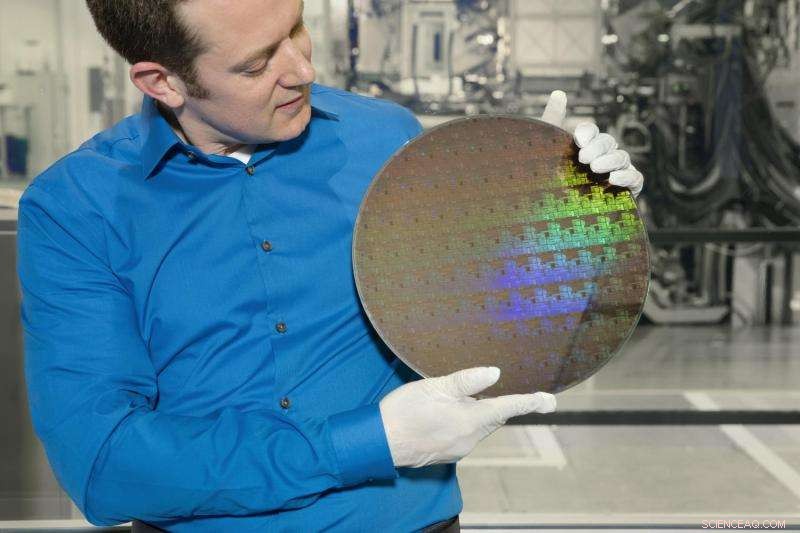

IBMs forskare Nicolas Loubet har en skiva med chips med 5 nm silikon-nanoskiktstransistorer tillverkade med en industri-första process som kan leverera 40 procent prestandaförbättring vid fast effekt, eller 75 procent energibesparing vid matchad prestanda. Kredit:Connie Zhou

IBM, dess Research Alliance-partners Globalfoundries och Samsung, och utrustningsleverantörer har utvecklat en industriförst process för att bygga kiseltransistorer för nanoskivor som möjliggör 5 nanometer (nm) chips. Detaljerna i processen kommer att presenteras vid Symposia on VLSI Technology and Circuits -konferensen 2017 i Kyoto, Japan. På mindre än två år sedan utvecklingen av ett 7nm testnodchip med 20 miljarder transistorer, forskare har banat väg för 30 miljarder switchar på ett fingernagel-chip.

Den resulterande ökningen av prestanda kommer att hjälpa till att påskynda kognitiv datoranvändning, Internet of Things (IoT), och andra dataintensiva applikationer levererade i molnet. Energibesparingarna kan också innebära att batterierna i smartphones och andra mobilprodukter kan hålla två till tre gånger längre än dagens enheter, innan den behöver laddas.

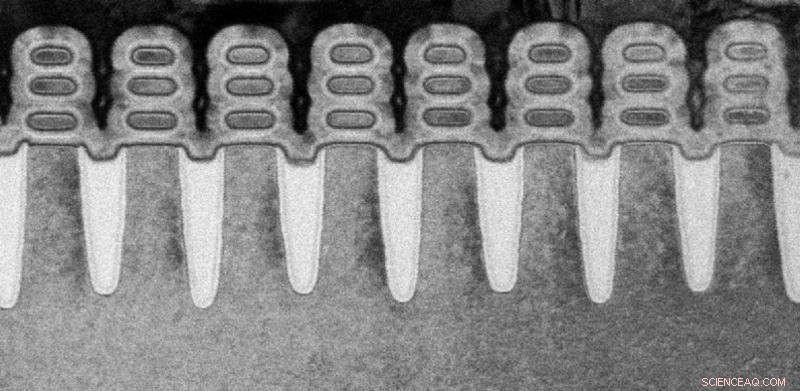

Forskare som arbetar som en del av den IBM-ledda forskningsalliansen vid SUNY Polytechnic Institute Colleges of Nanoscale Science and Engineerings NanoTech Complex i Albany, NY uppnådde genombrottet genom att använda staplar av kiselnanoark som enhetsstrukturen för transistorn, istället för den vanliga FinFET-arkitekturen, som är ritningen för halvledarindustrin upp genom 7nm nodteknologi.

"För att näringslivet och samhället ska möta kraven på kognitiv och molnbaserad datoranvändning under de kommande åren, framsteg inom halvledarteknik är avgörande, sade Arvind Krishna, senior Vice President, Hybridmoln, och regissör, IBM Research. "Det är därför IBM aggressivt strävar efter nya och annorlunda arkitekturer och material som tänjer på gränserna för denna industri, och för dem till marknaden inom teknologier som stordatorer och våra kognitiva system."

IBM -forskare vid SUNY Polytechnic Institute Colleges of Nanoscale Science and Engineering’s NanoTech Complex i Albany, NY förbered testwafers med 5nm silikon nanosheettransistorer, laddas i den främre öppningen unified pod, eller FOUPs, att testa en industri-första process för att bygga 5nm transistorer med kisel nanosheets. Kredit:Connie Zhou

Transistordemonstrationen av kisel nanoskivor, som beskrivs i Research Alliance-dokumentet Stacked Nanosheet Gate-All-Around Transistor för att möjliggöra skalning bortom FinFET, och publicerad av VLSI, bevisar att 5nm chips är möjliga, kraftfullare, och inte så långt borta i framtiden.

Jämfört med den ledande 10nm-tekniken på marknaden, en nanoarkbaserad 5nm-teknik kan ge 40 procent prestandaförbättring vid fast effekt, eller 75 procent energibesparing vid matchad prestanda. Denna förbättring möjliggör ett betydande uppsving för att möta de framtida kraven på system med artificiell intelligens (AI), virtuell verklighet och mobila enheter.

Bygga en ny switch

"Det här tillkännagivandet är det senaste exemplet på den forskning i världsklass som fortsätter att växa fram ur vårt banbrytande offentlig-privata partnerskap i New York, sa Gary Patton, CTO och chef för Worldwide R&D på Globalfoundries. "När vi gör framsteg mot att kommersialisera 7nm 2018 vid vår Fab 8-tillverkningsanläggning, vi driver aktivt nästa generations teknik på 5 nm och därefter för att behålla ledarskap inom teknik och göra det möjligt för våra kunder att producera en mindre, snabbare, och mer kostnadseffektiv generering av halvledare."

På bilden:en skanning av IBM Research Alliances 5nm transistor, byggd med en industriförst process för att stapla nanoark av kisel som enhetsstrukturen – vilket uppnår en skala på 30 miljarder switchar på ett fingernagel-chip som kommer att leverera betydande kraft- och prestandaförbättringar jämfört med dagens toppmoderna 10nm-chips. Kredit:IBM

IBM Research har utforskat nanosheet-halvledarteknologi i mer än 10 år. Detta arbete är det första i branschen som demonstrerar möjligheten att designa och tillverka staplade nanoarkenheter med elektriska egenskaper överlägsna FinFET-arkitektur.

Samma extrema ultravioletta (EUV) litografimetod som användes för att producera 7nm-testnoden och dess 20 miljarder transistorer applicerades på nanosheettransistorarkitekturen. Med EUV litografi, bredden på nanoarken kan justeras kontinuerligt, allt inom en enda tillverkningsprocess eller chipdesign. Denna justerbarhet tillåter finjustering av prestanda och effekt för specifika kretsar – något som inte är möjligt med dagens FinFET-transistorarkitekturproduktion, som begränsas av dess strömförande fenhöjd. Därför, medan FinFET -chips kan skala till 5 nm, Att bara minska mängden utrymme mellan fenorna ger inte ökat strömflöde för ytterligare prestanda.

"Dagens tillkännagivande fortsätter det offentlig-privata modellsamarbetet med IBM som ger SUNY-Polytechnic energi, Albanys, och staten New Yorks ledarskap och innovation när det gäller att utveckla nästa generations teknik, "sa Dr Bahgat Sammakia, Interimspresident, SUNY Polytechnic Institute. "Vi tror att aktiveringen av den första 5nm-transistorn är en viktig milstolpe för hela halvledarindustrin när vi fortsätter att driva oss bortom begränsningarna för våra nuvarande möjligheter. SUNY Polys partnerskap med IBM och Empire State Development är ett perfekt exempel på hur industri, Regering och akademi kan framgångsrikt samarbeta och ha en bred och positiv inverkan på samhället."

En del av IBM:s 3 miljarder dollar, femårig investering i chip FoU (tillkännagiven 2014), Beviset på att nanosheetarkitektur skalar till en 5nm-nod fortsätter IBMs arv av historiska bidrag till kisel- och halvledarinnovation. De inkluderar uppfinningen eller första implementeringen av encells-DRAM, Dennards skalningslagar, kemiskt förstärkta fotoresister, kopplingsledningar, Silikon på isolator, ansträngd ingenjörskonst, mikroprocessorer med flera kärnor, nedsänkningslitografi, höghastighets SiGe, High-k gate dielektrik, inbäddat DRAM, 3-D spånstapling och luftgapsisolatorer.