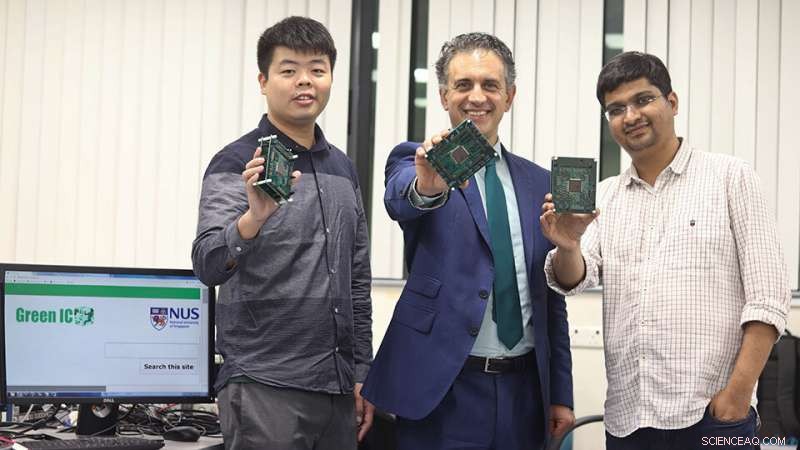

Assoc Prof Massimo Alioto (mitten) och hans teammedlemmar Lin Longyang (vänster) och Saurabh Jain (höger) visar upp prototyperna för att testa kiselchips för att visa mycket flexibel kraft och prestanda, överträffar branschstandardspänningsskalning. Kredit:National University of Singapore

Ett team av forskare från NUS har uppfunnit en ny klass av omkonfigurationstekniker som på ett anpassningsbart sätt ökar både minsta strömförbrukning och maximala prestanda för digitala kretsar, långt bortom vanlig spänningsskalning. Sådan utökad anpassning gör att digitala kiselchips fungerar vid lägre effekt under normal användning, och vid högre prestandanivå vid behov.

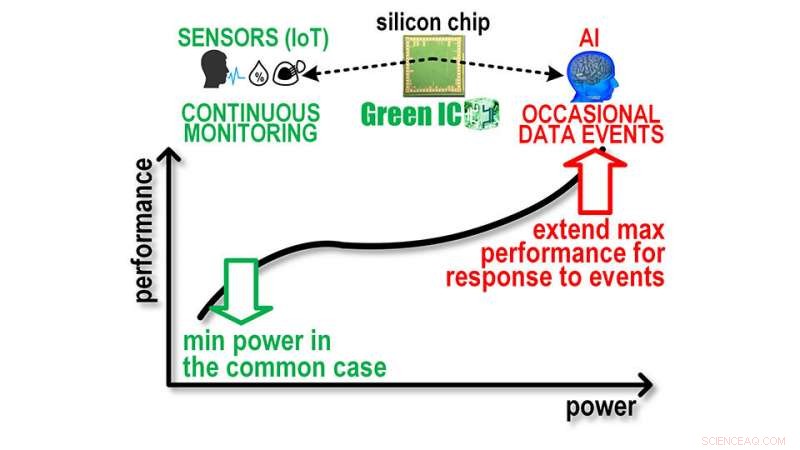

Detta förlänger batteriets livslängd under osäker strömtillgänglighet i system som drivs av skördare (t.ex. solceller) eller laddningsbara batterier, samtidigt som den levererar högre topprestanda för att utföra on-chip-dataanalys vid händelse av intressanta händelser. Detta är en viktig möjliggörare för applikationer som Internet of Things (IoT), artificiell intelligens (AI), bärbara och biomedicinska anordningar.

"Våra omkonfigureringstekniker introducerar oöverträffad anpassningsförmåga till fluktuerande strömtillgänglighet och prestandabehov. Jämfört med branschstandardspänningskalningstekniken, mätningar på flera testchips i vårt laboratorium har visat att sådan anpassning förlänger batteriets livslängd för en mobil eller bärbar enhet med 1,5 gånger, samtidigt som toppeffekten fördubblas. Våra tekniker kan också användas för att ytterligare minimera batteriet med samma faktor, samtidigt som batteriets livslängd bibehålls, "förklarade docent Massimo Alioto från NUS Engineering. Han är ledare för NUS Green IC Group som ligger bakom detta tekniska genombrott.

Han lade till, "Som ytterligare fördel, kraftöverföringsmångsidigheten hos våra kretstekniker gör det möjligt för halvledarföretag att förenkla sin chipportfölj och minska designkostnaden, eftersom samma digitala design kan återanvändas inom ett brett spektrum av applikationer och marknader. "

De föreslagna teknikerna har lett till demonstration av acceleratorer och processorer (t.ex. Snabb Fourier Transform, ARM -processorer) med minimal energiförbrukning hittills rapporterad. Forskningen bakom de nya teknikerna har fått stöd av ledande halvledarföretag (Intel, TSMC) samt Singapore Ministry of Education och National Research Foundation of Singapore.

Data- och klockvägsanpassning:Uppnår både låg minimiförbrukning och högre topprestanda

Mest avancerade mobil, IoT- och AI-applikationer kräver en flexibel och bred avvägning mellan den genomsnittliga effekten (dvs. Batteri-liv), och den maximala prestanda som avgör systemets lyhördhet (t.ex. när skärmen berörs, eller utföra dataanalys när en sensor producerar data av intresse).

För närvarande, dynamisk spänningsskalning är guldstandarden för att möjliggöra sådan flexibilitet. Att arbeta med spänningar runt 1 V leder till maximal prestanda och energiförbrukning, minskning till 0,4-0,5 V sänker energiförbrukningen med fyra till fem gånger och saktar ner hastigheten med nästan 10 gånger. Nackdelen med detta tillvägagångssätt är att spänningsskalning i allmänhet gäller en fast digital arkitektur, även om den optimala arkitekturen för energiförbrukning och prestanda beror på den antagna spänningen.

De adaptiva digitala kretsarna som NUS -teamet visar kan förlänga batteritiden för intelligenta kiselchips genom att minska strömförbrukningen vid normal användning, samtidigt som prestandan skalas upp för att snabbt svara på tillfälliga datahändelser. Kredit:National University of Singapore

NUS -uppfinningen överträffar spänningsskalning eftersom dess kretsomkonfiguration möjliggör bättre matchning mellan arkitekturen och den antagna spänningen, och därmed kan ytterligare minskning av energiförbrukningen och förbättringar av prestanda vid olika spänningar uppnås.

Docent Alioto sa, "Vår uppfinning möjliggör omkonfigurering av både" datavägen "där den faktiska behandlingen utförs, och "klockvägen" som distribuerar klocksignalen för att orkestrera de olika bearbetningsuppgifterna. I båda fallen, deras grundläggande byggstenar slås flexibelt ihop eller delas för att skapa data- och klockvägsstrukturen som förbättrar antingen energieffektivitet eller prestanda vid en given spänning. "

Jämfört med konventionell spänningsskalning, den strategi som föreslås av NUS Green IC -gruppen gör digitala kretsar mer mångsidiga och anpassningsbara, möjliggör samtidig optimering i båda ändar av effekt-spektrumet.

Teknisk bok och en komplett verktygskedja tillgänglig för allmänheten

För att dela fördelarna med teamets nya teknik med både industri och forskargrupper över hela världen, en teknisk bok har nyligen släppts för att ge bakgrund och detaljer om kiselchipsimplementeringen av processorer, acceleratorer och on-chip-minnen. Ett automatiserat designflöde har också skapats och publicerats offentligt via GitHub (Besök www.green-ic.org/).

"I vår bok, vi introducerade och demonstrerade designmetoder med enbart kommersiella designverktyg, som är integrerade i ett sammanhängande designflöde där omkonfigurering av klocka och datavägar integreras på ett plug-and-play-sätt. Vi är glada över att kunna dela programvarukoden på ett open source-sätt för att möjliggöra massiv och snabb användning av våra nya tekniker inom den kommersiella sektorn och inom akademisk forskning, "kommenterade docent Alioto.

Nästa steg

NUS-forskargruppen undersöker nu utvecklingen av nya klasser av intelligenta kiselsystem som möjliggör extremt bred effektprestanda-anpassning i AI-acceleratorer inbäddade i avkänning av kiselchips för IoT. Detta kommer att leda till nästa generations system som alltid är tillgängliga, samtidigt som de snabbt kan svara på externa händelser med mycket betydande beräkningsprestanda.

I deras arbete, teamet strävar efter att möjliggöra anpassning av effektprestanda genom drop-in-tekniker och designmetoder i befintliga systemarkitekturer. Detta gör det möjligt att uppnå effektfördelar utan att störa designekosystemet, vilket möjliggör ett snabbt och massivt införande av nästa generations intelligenta system.