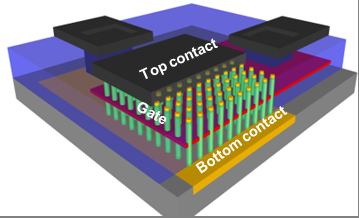

Diagram över en 3D-nanotransistor som visar grinden (röd) som omger de vertikala nanotrådarna (grön) och separerar kontakterna i ändarna av varje nanotråd (beige). Kredit:© X-L Han och G. Larrieu

Ett nytt genombrott kan tänja på gränserna för miniatyriseringen av elektroniska komponenter längre än man tidigare trott var möjligt. Ett team vid Laboratoire d'Analyse et d'Architecture des Systèmes (LAAS) och Institut d'Électronique, de Microélectronique et de Nanotechnologie (IEMN) har byggt en nanometrisk transistor som visar exceptionella egenskaper för en enhet av dess storlek. För att uppnå detta resultat, forskarna utvecklade en ny tredimensionell arkitektur bestående av en vertikal nanotrådsuppsättning vars ledningsförmåga styrs av en grind som endast mäter 14 nm i längd.

Publicerad i Nanoskala , dessa fynd öppnar vägen mot alternativ till de plana strukturerna som används i mikroprocessorer och minnesenheter. Användningen av 3D-transistorer kan avsevärt öka kraften hos mikroelektroniska enheter.

Mikroelektronikens "byggstenar" transistorer består av en halvledarkomponent, kallad kanal, koppla samman två terminaler. Strömflödet mellan dessa terminaler styrs av en tredje terminal, kallas port. Fungerar som en switch, grinden avgör om transistorn är på eller av. Under de senaste 50 åren, transistorer har stadigt minskat i storlek, möjliggör utvecklingen av allt kraftfullare mikroelektroniska enheter. Dock, det är allmänt överens om att dagens transistorer, med sin plana arkitektur, närmar sig gränserna för miniatyrisering:det finns en minimistorlek under vilken grindkontrollen över kanalen blir mindre och mindre effektiv. Särskilt, läckströmmar börjar störa de logiska operationerna som utförs av transistormatrisen. För att övervinna detta problem, forskare runt om i världen undersöker alternativ som gör att kapplöpningen för miniatyrisering kan fortsätta.

Ett team av forskare vid LAAS och IEMN har nu byggt den första verkligt tredimensionella nanometriska transistorn. Enheten består av en tät vertikal nanotrådsuppsättning av cirka 200 nm i längd som länkar samman två ledande ytor. En kromport omger helt varje nanotråd och styr strömflödet, vilket resulterar i optimal transistorstyrning för ett system av denna storlek. Porten är bara 14 nm lång, jämfört med 28 nm för transistorerna i dagens chips, men dess förmåga att styra strömmen i transistorns kanal uppfyller kraven för modern mikroelektronik.

Denna arkitektur kan leda till utvecklingen av mikroprocessorer där transistorerna staplas ihop. Antalet transistorer i ett givet utrymme skulle alltså kunna ökas avsevärt, tillsammans med prestandakapaciteten hos mikroprocessorer och minnesenheter. En annan betydande fördel med dessa komponenter är att de är relativt enkla att tillverka och inte kräver högupplöst litografi. Dessutom, dessa 3D-transistorer skulle lätt kunna integreras i de konventionella mikroelektroniska enheterna som används av industrin idag.

Ett patent har lämnats in för dessa transistorer. Forskarna planerar nu att fortsätta sina ansträngningar för att ytterligare minska storleken på grinden, som de tror skulle kunna göras mindre än 10 nm samtidigt som de ger tillfredsställande kontroll över transistorn. Dessutom, teamet letar efter industriella partners för att hjälpa till att designa framtidens elektroniska enheter med hjälp av 3D-arkitekturen hos dessa nya transistorer.