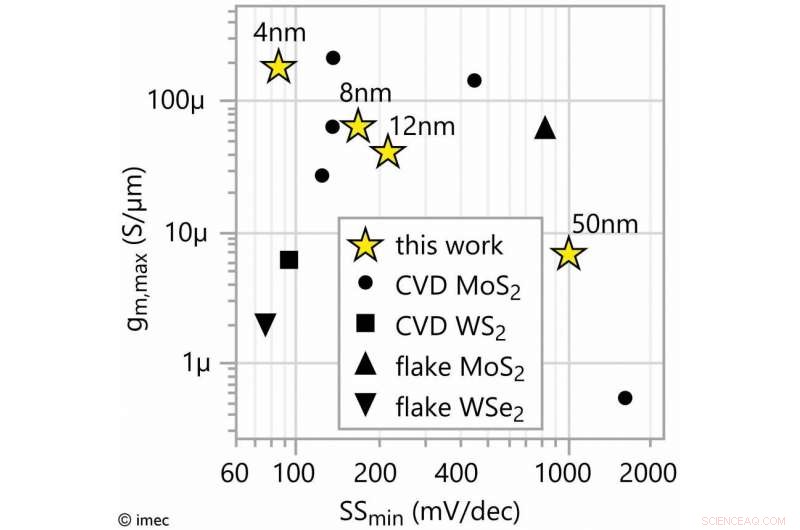

Benchmarkstudie:imecs enheter med 4nm, 8 nm, 12nm HfO2 och 50nm SiO2 har utmärkt kombination av gmmax och SSmin jämfört med litteratur. Upphovsman:IMEC

Vid årets IEEE International Electron Devices Meeting (7-11 december 2019), imec rapporterar en djupgående studie av skalade transistorer med MoS 2 och visar bästa enhetsprestanda hittills för sådant material.

MoS 2 är ett 2-D-material, vilket innebär att den kan odlas i stabil form med nästan atomtjocklek och atomprecision. Imec syntetiserade materialet ner till monoskikt (0,6 nm tjocklek) och tillverkade enheter med skalad kontakt och kanallängd, så liten som 13 nm respektive 30 nm. Dessa mycket skalade dimensioner, kombinerat med skalad gateoxid -tjocklek och hög K -dielektrikum, har möjliggjort demonstrationen av några av de bästa enhetsprestationerna hittills. Viktigast, dessa transistorer möjliggör en omfattande studie av grundläggande enhetsegenskaper och kalibrering av TCAD-modeller. Den kalibrerade TCAD -modellen används för att föreslå en realistisk väg för prestationsförbättring. Resultaten som presenteras här bekräftar potentialen för 2-D-material för extrem transistorskalning-vilket gynnar både högpresterande logik och minnesapplikationer.

Teoretiska studier rekommenderar 2-D-material som det perfekta kanalmaterialet för extrem transistorskalning eftersom endast små korta kanaleffekter förväntas jämfört med nuvarande Si-baserade enheter. Tips om denna potential har redan publicerats med enstaka transistorer byggda på naturliga flingor av 2-D-material.

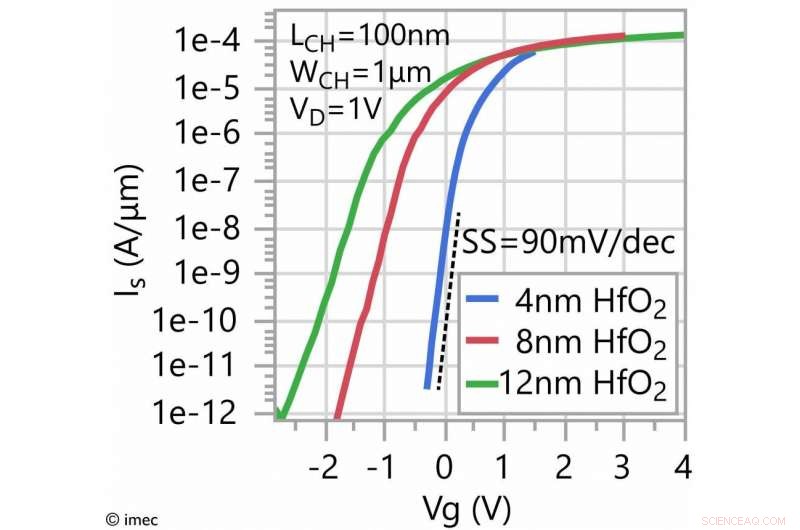

TEM-bilder som visar (a) 3 monolager MoS2-kanal, med kontaktlängd 13nm och kanallängd 29nm Överföringsegenskaper har förbättrat undergränssving (SS) med tunnare HfO2. Upphovsman:IMEC

För första gången, imec har testat dessa teoretiska fynd genom en omfattande uppsättning 2-D-materialbaserade transistordata. Enheterna med det minsta fotavtrycket har en kanallängd på 30 nm och <50 nm kontaktpunkt. ON-ström så hög som 250 µA/µm har visats med 50 nm SiO2-styrdielektrikum. På ström på ~ 100 µA/µm och en utmärkt SSmin på 80mV/dec (för VD =50mV) har visats med 4nm HfO2 i en backgated konfiguration. Enhetens prestanda påverkas inte av kontaktlängdskalning, bekräftar att bärare injiceras från kanten av kontaktmetallen direkt in i kanalen, i linje med TCAD -simuleringar. Arbetet bekräftar att TCAD -modeller fångar stora delar av enhetens fysik och guidar experimentell validering och kartläggning av applikationsutrymmet. En del av uppsatsen som presenteras på IEDM, är dedikerad till att ställa in vägen för enhetsoptimering för att nå Si-liknande prestandamål.

"Även om det fortfarande är en storleksordning från Si -transistorer, vi har tagit med våra MOSFET-enheter till en värld där de visar lovande prestanda för framtida logik- och minnesapplikationer, "säger Iuliana Radu, chef för Exploratory and Quantum Computing imec. "För att överbrygga denna storleksordning, vi har identifierat en väg för systematiska förbättringar som en ytterligare minskning av portoxidets tjocklek, implementering av en dubbelgrindad arkitektur, och ytterligare minskning av kanal- och gränssnittsdefekter. Vi överför denna insikt till vår 300 mm platta för transistorer med 2-D-material, som tillkännagavs vid förra årets IEDM. "

Överföringsegenskaperna har förbättrat svängning under tröskelvärdet (SS) med tunnare HfO2. Upphovsman:IMEC

"Som ett världsledande forsknings- och innovationsnav, det är imecs roll att driva enhetens skalning mot den yttersta gränsen. Vi tacklar denna utmaning genom att undersöka olika skalningsalternativ, ger optimala projektioner, och vägleder industrin att anta de föreslagna lösningarna, sade Luc Van den hove, imec VD. "Våra partners förväntar oss att vi ska gå före och stödja dem i att förverkliga sina färdplaner genom att demonstrera potentialen hos innovativa koncept och nya material. Det är därför jag är så glad att vi har visat utmärkt prestanda i ultrakaliga enheter med 2-D-material , och en trovärdig väg till ytterligare förbättringar som syftar till massproduktion i industriella 300 mm fabriker."