Kredit:Samsung

"Nanometerprocessen handlar om utrymmet mellan transistorerna monterade på ett substrat på nanometernivå, " sa Puls .

"Ju smalare avstånd, desto fler chips kan pressas in för att öka datorkraften och energieffektiviteten. En nanometer motsvarar en tiotusendel av diametern på ett människohår."

På Samsung Foundry Forum i Santa Clara, Kalifornien, företaget försökte nyligen imponera på framsteg som det har gjort inom 3nm gate-all-around (GAA) processutveckling.

Samsung Foundry introducerar nu MBCFET (multi bridge channel FET). Detta består av flerstaplade nanoark. Med nanoarkbildningen, en större ström per stack är möjlig, sa SamMobile .

ExtremeTech beskrev tillkännagivandet som om "en ny, utvecklad transistorarkitektur" som kommer från Samsung Foundry - som involverar "nanosheets"-metoden för dess 3nm-nod.

(Från Samsungs redaktion:"Konventionell GAA baserad på nanotråd kräver ett större antal stackar på grund av sin lilla effektiva kanalbredd. Å andra sidan, Samsungs patenterade version av GAA, MBCFET (Multi-Bridge-Channel FET), använder en nanoarkarkitektur, möjliggör större ström per stack.")

Bloggen CNXSoft belyser ytterligare varför övergången från nanotrådar till nanoark.

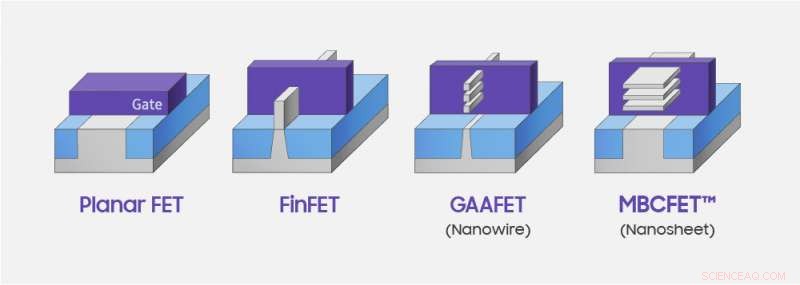

"Vi läser ofta att nya processorer är tillverkade med en FinFET-process. Den nya processen skapades på grund av korta kanaleffekter i traditionella plana transistorer, och FinFET (Fin Field-effect transistor) introducerades för att möjliggöra ytterligare spänningsskalning men med processnoden som blev mindre och mindre, elektrostatiska effekter började orsaka problem."

Att använda GAA (Gate All Around) nanotrådar för att begränsa dessa effekter togs som ett svar, men de är tydligen väldigt svåra att integrera i kisel, sa bloggen, så det slutade med att Samsung använde tunna lager (nanosheets) istället för nanotrådar, "möjliggör större ström per spår i deras GAA-implementering som kallas MBCFET (Multi-Bridge Channel Field-Effect Transistor)."

För dem som behöver bearbeta överbelastningen av akronymer, Ramish Zafar in Wccftech tog sina läsare med på Samsungs resa. 1. Samsung samarbetade med IBM för GAAFET-processnoder (Gate-All-Around). 2. Nu har företaget meddelat sina anpassningar till den tidigare processen, och detta är MBCFET.

Zafar hade mer att säga om MBCET. "I motsats till traditionella FinFET-designer, GAAFET tillåter grindmaterialet att omge kanalen från alla sidor. Samsung hävdar att MBCFET:s design kommer att förbättra processens on-off-beteende, och tillåter processorer att minska driftsspänningen under 0,75V. En avgörande punkt för MBCFET är att processen är helt kompatibel med FinFET-designer och inte kräver några nya verktyg för tillverkning."

Kredit:Samsung

Hur, fastän, ingår alla dessa goda nyheter i företagets utvecklingsplaner. När kan vi förvänta oss att se teknik i aktion? Joel Hruska tog upp detta i ExtremeTech .

"På sitt Samsung Foundry Forum denna vecka, Samsung deklarerade att dess produktdesignsats för 3nm-chips nu är i alfa, efter att ha nått utvecklingsmilstolpen på 0,1. Samsung planerar att lansera en uppsjö av processnoder under de kommande åren, med utvecklingsspår planerade för 7nm, 6nm, 5nm, 4nm, och ja, 3nm."

Hruska tillade, "Förbättringarna för 3nm jämfört med 7nm är ganska bra, men den här noden kommer faktiskt inte att skickas på länge." Hans artikel innehåller ett diagram som visar utvecklingen som kommunicerats av Samsung.

© 2019 Science X Network