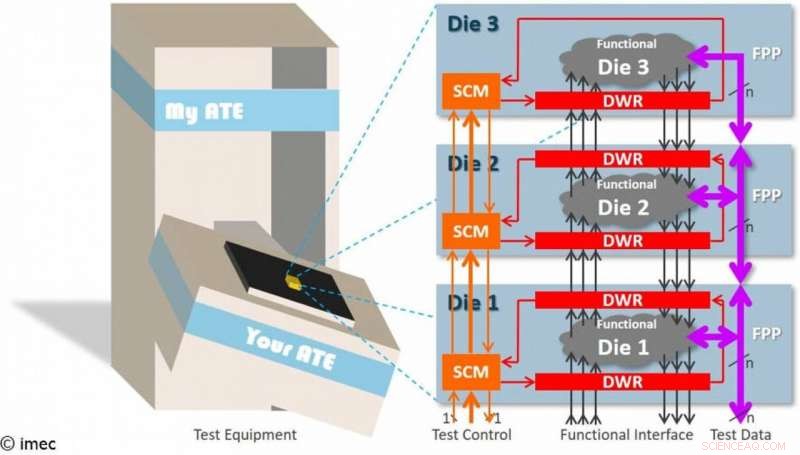

Konceptuellt tvärsnitt av en 3D-IC som består av tre staplade formar. Testutrustning skickar teststimuli till och tar emot testsvar från 3D-IC:s externa gränssnitt som finns längst ner i stacken. IEEE Std 1838™-2019 design-for-test-elementen i de olika formarna bildar en konsekvent teståtkomstarkitektur genom vilken testutrustningen kan komma åt varje form i stacken. Kredit:IMEC

Denna vecka, IMEC, ett världsledande forsknings- och innovationsnav inom nanoelektronik och digital teknik, meddelade att IEEE Std 1838TM-2019 – som nyligen godkänts av IEEE Standards Association – kommer att inkluderas i IEEE Xplore Digital Library från februari 2020 och framåt. Den nya standarden tillåter formtillverkare att designa formar som, om den uppfyller denna standard, utgöra, en gång staplad i en 3-D-IC av en stackintegrator, en konsekvent arkitektur för teståtkomst på stacknivå. Standardiseringsarbetet för 3-D-DfT (design-for-test) initierades av IMEC.

3-D-IC:er utnyttjar den vertikala dimensionen för ytterligare integration genom att stapla matriser ovanpå varandra som ett sätt att hålla farten i Moores lag igång. Eric Beyne, fellow och program director 3-D System Integration på IMEC, säger, "Framsteg inom waferbearbetning och stackmonteringsteknologier skapar en mängd olika stackarkitekturer. Detta orsakar en kraftig ökning av antalet potentiella ögonblick då testning av tillverkningsfel kan utföras:förbindning (före stapling), mid-bond (på partiella staplar), post-bond (på hela staplar), och sluttest (på förpackade 3-D-IC). Testutrustningen kontaktar IC:er via dess externa gränssnitt genom sondnålar eller vid testuttaget. I en stack, det externa gränssnittet ligger vanligtvis i bottenmatrisen i stacken. För att testutrustningen ska kunna leverera teststimuli till och ta emot svar från de olika matriserna uppe i stacken, samarbete från de underliggande stansarna krävs för att ge teståtkomst till tärningen som för närvarande testas."

En IEEE-arbetsgrupp för att standardisera 3-D-DfT grundades 2011 av Erik Jan Marinissen, vetenskaplig chef vid IMEC i Leuven, Belgien och han fungerade som dess första ordförande. På senare år har Adam Cron, chefsingenjör inom forskning och utveckling i designgruppen på Synopsys, har varit den drivande kraften som nuvarande ordförande i arbetsgruppen.

Amit Sanghani, vice vd för teknik i designgruppen på Synopsys i Mountain View, Kalifornien, USA sade:"3-D-IC är en viktig teknik för att leverera nästa våg av innovation när industrin skalar förbi 7nm. För närvarande, formen kan komma från olika leverantörer med osammanhängande DfT-arkitekturer.

Den nya standarden består av tre huvudelement. (1) DWR, dynomslagsregistret:skanna kedjor vid gränsen för varje dyn i stapeln för att möjliggöra modulär testning av insidan av varje dyn och av sammankopplingarna mellan varje par av intilliggande dyn. (2) SCM, den seriella kontrollmekanismen:en enbits testkontrollmekanism som transporterar instruktioner in i stapeln för att kontrollera testlägena för de olika formomslagen. (3) FPP, den valfria flexibla parallellporten, dvs. en skalbar flerbitars teståtkomstmekanism för att effektivt transportera upp och ner i formstacken de stora datamängder som vanligtvis är förknippade med produktionstest. Medan DWR och SCM är baserade på befintliga DfT-standarder, FPP är verkligen ny för IEEE Std 1838.

Wolfgang Meyer, senior group director R&D på Cadence Design Systems i San Jose, Kalifornien, U.S., säger, "En DfT-standard som IEEE Std 1838 är viktig för industrin. Formtillverkare vet vad de måste tillhandahålla, och stackintegratörer vet vad de kan förvänta sig. Dessutom, EDA-leverantörer som Cadence kan fokusera sitt verktygsstöd på arkitekturer som är kompatibla med den nya standarden. Det är bra att det finns en viss användardefinierad skalbarhet med standarden eftersom 3-D-IC-fältet är så brett att en stel standard "one-size-fits-all" skulle inte fungera."

Junlin Huang, chef för ett 150 personer starkt DfT-team av HiSilicon i Shenzhen, Kina, säger, "Per år, vi gör DfT-insättning och automatisk testmönstergenerering (ATPG) för tiotals mycket stora och komplexa digitala chipdesigner i de mest avancerade teknologierna. Nu, dessa produkter börjar använda 3D-teknik och mitt DfT-team måste vara redo att hantera de associerade DfT- och ATPG-utmaningarna. IEEE Std 1838 kommer att hjälpa oss med den uppgiften."

Från februari 2020 och framåt den nya standarden IEEE Std 1838 kommer att vara tillgänglig via IEEE Xplore för abonnenter av IEEE-standarder såväl som för köp till alla andra.