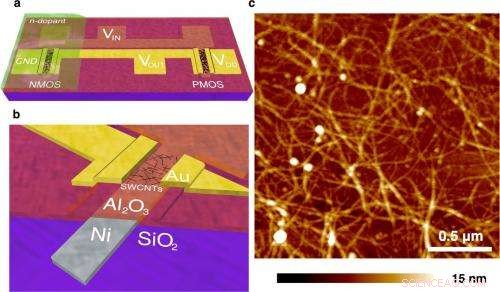

Illustrationer av (a) CNT CMOS-växelriktaren och (b) ett tvärsnitt av en individuell CNT-transistor, inklusive en 25 nm tjock Ni-port som möjliggör ultralåg strömförbrukning. (c) Atomkraftmikroskopibild av CNT -filmmorfologin i transistorkanalregionen. Kredit:Geier, et al. ©2013 American Chemical Society

(Phys.org) – Forskare har demonstrerat en ny kolnanorör (CNT)-baserad logikenhet som förbrukar bara 0,1 nanowatt (nW) i sina statiska PÅ och AV-lägen, representerar det lägsta rapporterade värdet med 3 storleksordningar för CNT-baserade CMOS-logiska enheter. Enheten kan fungera som en byggsten för stora ytor, ultralågeffekt CNT-logikkretsar som kan användas för att realisera en mängd olika nanoelektroniktillämpningar.

Forskarna, Michael L. Geier, et al., vid Northwestern University i Evanston, Illinois, och University of Minnesota i Minneapolis, har publicerat sin uppsats om subnanowatt CNT-logiken i ett nyligen utgåva av Nanobokstäver .

"En modern integrerad krets har mer än 1 miljard transistorer, " medförfattare Mark C. Hersam, professor i materialvetenskap och teknik, Kemi, och medicin vid Northwestern University, berättade Phys.org . "Följaktligen, effektförlusten per transistor måste vara mycket låg för att hela kretsen ska ha en rimlig strömförbrukning. Faktiskt, det är allmänt accepterat att strömförbrukning är den viktigaste begränsande faktorn för att uppnå ytterligare ökningar av komplexiteten (dvs. antal transistorer) i integrerade kretsar."

Som forskarna förklarar, en av de största fördelarna med CMOS-arkitektur är att den har en naturligt låg strömförbrukning. Denna fördel kommer från det faktum att till skillnad från andra logiska arkitekturer, en av de två typerna av transistorer (p-typ eller n-typ) stängs av under stationära förhållanden i varje logisk grind i CMOS-enheter.

För att fullt ut dra nytta av denna potential för extremt låg strömförbrukning, p-typ och n-typ transistorer måste ha exakt avstämda och väl separerade tröskelspänningar, vilka är spänningsnivåerna som avgör om enheten är PÅ eller AV. Än så länge, denna fråga om tröskelspänningarna har inte behandlats, och forskarna här identifierade det som den viktigaste utmaningen som begränsar förverkligandet av mycket integrerad CNT-baserad CMOS-elektronik.

I deras studie, forskarna använde en metallgrindstruktur för att uppnå symmetriska och tydligt separerade tröskelspänningar för p-typ och n-typ CNT-transistorer, vilket resulterar i den ultralåga strömförbrukningen. I statiska tillstånd, där enheten är antingen PÅ eller AV, strömförbrukningen är mindre än 0,1 nW. I mitten av överföringstillståndet, när både p-typ och n-typ transistorer är samtidigt i ON-läge, spänningen når sin topp vid 10 nW.

Genom att ansluta flera CNT-transistorer i olika konfigurationer, forskarna visade inverter, NAND och NOR logiska grindar. I framtiden, dessa grindar kan integreras i komplexa kretsar, där de kan ge statisk energiförbrukning under nanowatt tillsammans med de andra fördelarna med CNT, såsom lösningsbearbetbarhet och flexibilitet.

"Vi arbetar nu med att göra mer komplicerade kretsar, där vi kommer att ha betydligt fler transistorer och kaskadkopplade logiska grindar, "Hersam sa." Vi har också ett intresse av att kombinera kolnanorör med andra framväxande nanoelektroniska material i vårt laboratorium (t.ex. molybdendisulfid [MoS 2 ])."

© 2013 Phys.org. Alla rättigheter förbehållna.