NUS Green IC-teamet:Dr Orazio Aiello (vänster) och docent Massimo Alioto (höger). Kredit:National University of Singapore

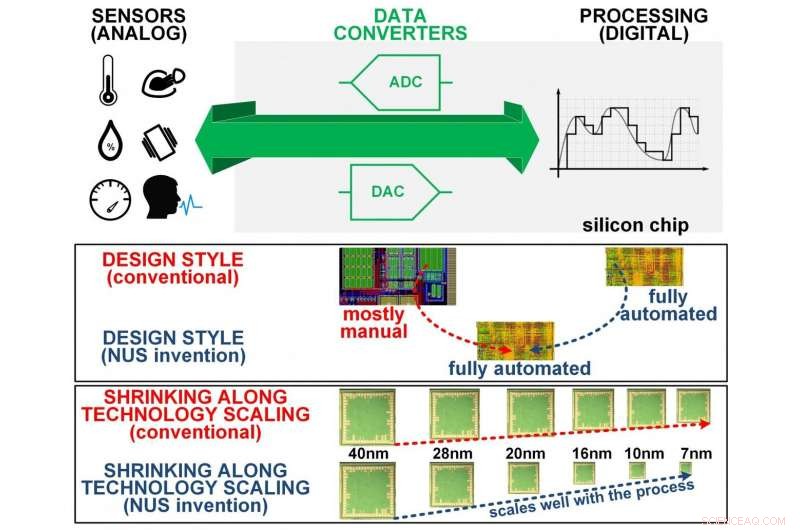

Forskargruppen Green IC vid avdelningen för elektro- och datorteknik vid National University of Singapores (NUS) tekniska fakultet uppfann en ny klass av digital-till-analog (DAC) och analog-till-digital omvandlare (ADC) som kan vara helt designad med en helautomatisk digital designmetod, tack vare dess helt digitala arkitektur (Fig. 1).

Jämfört med traditionella analoga arkitekturer och metoder, designens handläggningstid för dessa nya sensorgränssnitt reduceras från månader till timmar. Den drastiska minskningen av designansträngningen är mycket fördelaktig i kostnadskänsliga kiselsystem, såsom sensorer för Internet of Things (IoT). Den nya dataomvandlararkitekturen har också mycket låg komplexitet, minska kiselytan och därmed tillverkningskostnaden med minst 30 gånger, jämfört med konventionella konstruktioner.

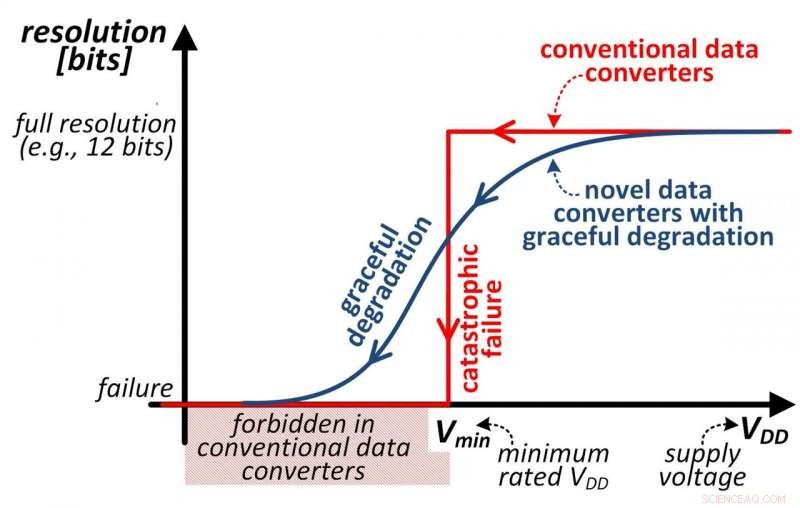

Sådana nya dataomvandlare uppvisar också den oöverträffade förmågan att graciöst försämra signaltroheten när dess matningsspänning eller klockfrekvens upplever stora fluktuationer (fig. 2). Sådana fluktuationer är vanliga i energiskördade IoT-sensorer, är att kraften som tas från den omgivande miljön (t.ex. solcell) är mycket oregelbunden. I tur och ordning, detta tillåter oavbruten sensorsignalövervakning även under ogynnsamma avverkningsförhållanden, och utan spänningsreglering. Istället, traditionella dataomvandlare lider av katastrofal upplösningsförsämring när matningsspänningen är under dess lägsta nominella värde Vmin (eller frekvensen överstiger dess maximala nominella värde) som i Fig. 2, behöver därför effektkrävande kretsar för spännings- och frekvensreglering.

Forskningen utfördes i samarbete med docent Paolo Crovetti från Politecnico di Torino i Italien, och stöds av Singapores utbildningsministerium och EU-kommissionen.

Mindre sensorgränssnitt, enklare och snabbare att designa

"Vår forskning omvandlar den traditionellt analoga och mestadels manuella designen av dataomvandlare till helautomatisk digital design, minska kiselarean med en storleksordning och designtiden med två storleksordningar, tillåta halvledarföretag att vara kostnadskonkurrenskraftiga samtidigt som de når marknader snabbare, " sa teamledaren docent Massimo Alioto, som kommer från institutionen för elektro- och datateknik vid NUS tekniska fakultet.

Katastrofala misslyckanden ersätts av graciös upplösningsförsämring i den nya klassen av konventionella dataomvandlare som uppfunnits av NUS-teamet. Detta gör det möjligt att drastiskt förenkla systemdesignen, undertrycker behovet av noggrann spänningsreglering. Kredit:National University of Singapore

Han lade till, "Att vara digital, våra sensorgränssnitt överförs enkelt över tillverkningsteknologier och applikationer, och kan nedsänkas i digitala kretsar för att undvika den traditionella ansträngning som krävs av deras integration på samma kiselchip." (Fig. 1).

NUS-teamet demonstrerade konceptet genom flera kiselchips som implementerade både DAC och ADC med extremt låg yta. Som ett exempel, en 12-bitars DAC tillverkad i 40nm standard CMOS-teknik har visats med en yta som är lika med diametern på ett hårstrå. Dess inneboende lättillgänglighet för teknologiska skalning gör att den krymper med ytterligare cirka 32 gånger när den implementeras i den för närvarande finaste tekniken (7 nm).

På samma gång, NUS-uppfinningen har visat sig möjliggöra dataomvandlare med hög upplösning (upp till 16 bitar), samtidigt som designenkelhet och kompakthet uppnås.

Teammedlem Dr. Orazio Aiello, som är gästforskare vid institutionen, sa, "Vårt team har introducerat ett nytt designparadigm som driver oss närmare den ultimata visionen om billiga, teknologiska skalbara och ultrakompakta IoT-enheter."

Oöverträffad robusthet ger ytterligare fördelar på systemnivå

NUS-innovationen förenklar integrerad systemdesign ytterligare, utnyttja den oöverträffade förmågan att motstå mycket betydande spännings- och frekvensfluktuationer, sålunda lättar på noggrannhetskraven i spännings- och frekvensgenerering.

Katastrofala misslyckanden ersätts av graciös upplösningsförsämring i den nya klassen av konventionella dataomvandlare som uppfunnits av NUS-forskarna. Kredit:National University of Singapore

Verkligen, konventionella dataomvandlare som arbetar med en matningsspänning under dess lägsta nominella värde (eller för höga klockfrekvens) upplever katastrofala fel, och därmed misslyckas med att utföra sin avsedda funktion (fig. 2). Tvärtom, de innovativa dataomvandlarna som uppfunnits av NUS-teamet uppvisar en graciös försämring av upplösningen och signaltroheten när matningsspänningen eller klockfrekvensen överskrider dess tillåtna intervall. Som ett exempel, en DAC designad för 1 V visades fungera korrekt vid halva denna spänning, samtidigt som dess upplösning försämras med endast 1 bit när matningsspänningen reduceras med avsevärt 0,3V.

Docent Prof Alioto sa, "Förmågan att ha graciös upplösningsförsämring under spännings- och frekvensöverskalning undertrycker behovet av komplexa kretslösningar som noggrant reglerar matningsspänningen och klockfrekvensen som används av dataomvandlare. Med andra ord, våra dataomvandlare är enklare att designa, och även förenkla systemet som de är anställda i."

Nästa steg

Teamet arbetar för närvarande på ett nytt paradigm som förvandlar traditionellt analoga och designintensiva kiselundersystem till digitala standardcellbaserade konstruktioner som stöds av helautomatiska designflöden, tänjer på gränsen för klassisk digitalt assisterad design. Denna forskningsstudie involverar flera grundläggande delsystem såsom förstärkare, oscillatorer, spännings- och strömreferenser, och många andra.

Forskargruppen strävar efter att förändra hur integrerade system utformas, möjliggör ultrasnabb, ultrakompakt och teknologibärbar design av hela system.