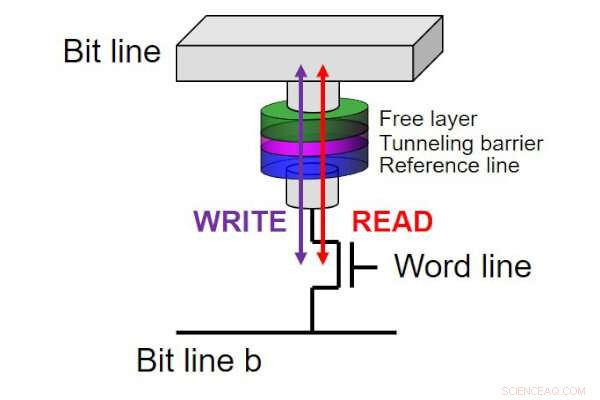

Schematisk bild av STT-MRAM-cell (Two Terminal Device). Kredit:CIES, Tohoku universitet

Forskare vid Tohoku University har tillkännagett demonstrationen av en höghastighets spin-orbit-torque (SOT) magnetoresistiv random access memory cell kompatibel med 300 mm Si CMOS-teknik.

Efterfrågan på lågeffekts- och högpresterande integrerade kretsar (IC) har ökat i takt med att enheter med artificiell intelligens (AI) och Internet-of-Things (IoT) blivit mer allmänt använda. Med nuvarande IC, rent CMOS-baserade minnen som inbäddat Flash-minne (eFlash) och statiskt random-access-minne (SRAM) är ansvariga för en hög andel strömförbrukning. För att sänka strömförbrukningen med bibehållen hög prestanda, magnetoresistiva direktminnen (MRAM) har utvecklats intensivt. Spin-överföring vridmoment MRAM (STT-MRAM) är det mest intensivt utvecklade MRAM. Stora halvledarföretag har nu meddelat att de är redo för massproduktion av STT-MRAM för eFlash-ersättning.

Forskare siktar på att ersätta SRAM med MRAM. För SRAM-ersättning, MRAM måste uppnå höghastighetsdrift över 500 MHz. För att möta efterfrågan, ett alternativt MRAM, så kallat spin-orbit torque MRAM (SOT-MRAM) föreslogs, vilket har flera fördelar för höghastighetsdrift. På grund av dessa fördelar, SOT-MRAM har också utvecklats; dock, de flesta laboratoriestudier fokuserar på grunderna för SOT-enheter. För att ersätta SRAM med SOT-MRAM, det krävs för att visa högpresterande SOT-MRAM-minnescell på ett 300 mm CMOS-substrat. Dessutom, det är nödvändigt att utveckla integrationsprocessen för SOT-MRAM, t.ex., termisk tolerans mot 400 °C glödgning, vilket är ett krav i standard CMOS back-end-of-line-processen.

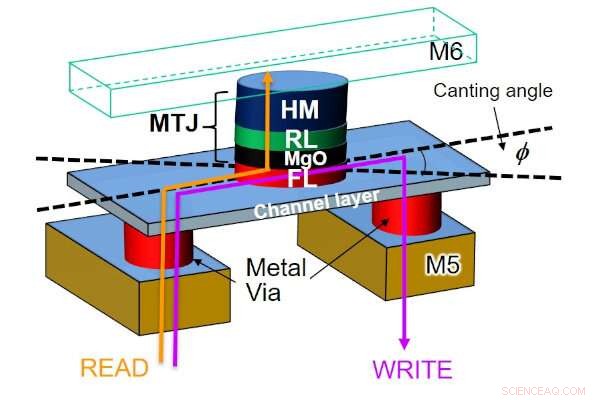

Ett schema över SOT-MRAM-cellen (Three Terminal Device) Kredit:CIES, Tohoku universitet

En schematisk vy av den snedställda SOT-MRAM-cellen. Kredit:CIES, Tohoku universitet

Forskargruppen ledd av professorerna Tetsuo Endoh och Hideo Ohno – den nuvarande presidenten för Tohoku University – har utvecklat en integrationsprocess för SOT-enheter som är kompatibla med 55 nm CMOS-teknik och tillverkade SOT-enheter på 300 mm CMOS-substrat. Den nyutvecklade SOT-enheten har samtidigt uppnått höghastighetsväxling ner till 0,35 ns och en tillräckligt hög termisk stabilitetsfaktor (E/k) B T 70) för icke-flyktiga höghastighetsminnesapplikationer med robusthet mot glödgning vid 400 °C. Baserat på denna prestation, forskargruppen har integrerat SOT-enheten med CMOS-transistorer och slutligen demonstrerat höghastighetsdrift i kompletta SOT-MRAM-minnesceller.

Dessa prestationer har tagit itu med frågorna för att göra SOT-MRAM praktiskt för kommersiella applikationer och därmed erbjuda ett sätt att ersätta SRAM med SOT-MRAM, som kommer att bidra till förverkligandet av högpresterande elektronik med låg strömförbrukning.

Resultaten kommer att presenteras vid 2019 IEEE International Electron Devices Meeting i San Francisco, 7-11 december, 2019.