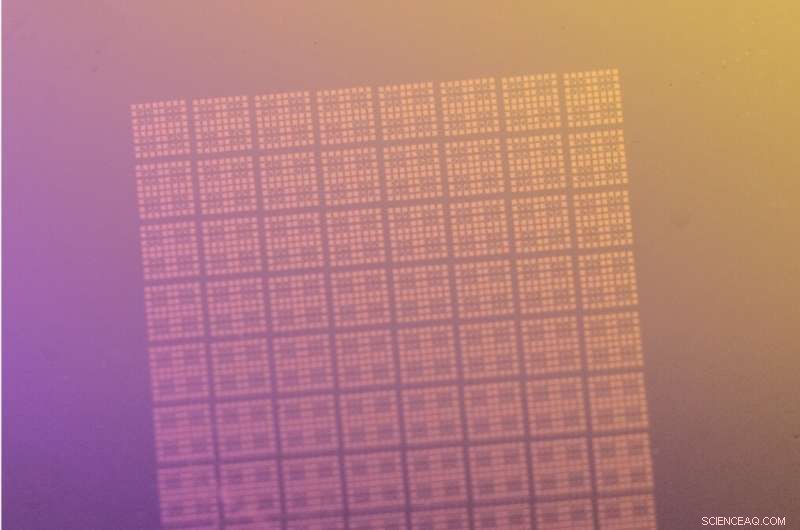

Bild på en enhetsmatris tillverkad med den metod som föreslagits av forskarna. Kredit:Li et al.

2-D halvledare kan ha mycket användbara applikationer, särskilt som kanalmaterial för lågeffekttransistorer. Dessa material uppvisar mycket hög rörlighet vid extrema tjocklekar, vilket gör dem till särskilt lovande alternativ till kisel vid tillverkning av elektronik.

Trots deras fördelar, att implementera dessa material i transistorer har hittills visat sig vara utmanande. Faktiskt, 2-D halvledare är av dinglande bindningsfri karaktär; Således, det är notoriskt svårt att deponera ultratunna dielektriska högk-grind (dvs. ämnen med dielektriska egenskaper eller isolatorer) på materialen via atomlagerdeposition (ALD), resulterar ofta i diskontinuerliga filmer.

Forskare vid Nanjing University i Kina har nyligen presenterat en ny strategi för att övervinna denna begränsning, slutligen tillåter avsättning av grinddielektrik på 2D-halvledare. I en tidning publicerad i Naturelektronik , de rapporterade den framgångsrika ALD av dielektriska högk-grind på 2-D-halvledare med användning av en molekylär kristall som ett ymplager.

"Vår forskning försöker lösa problemet med högkvalitativ gate dielektrisk integration för 2-D transistorer, "Xinran Wang, en av forskarna som genomförde studien, berättade TechXplore. "I toppmoderna Si-transistorer, den effektiva oxidtjockleken (EOT) har skalats ner till under 1 nm. För närvarande, det finns ett stort gap mellan 2D-material och Si när det gäller EOT, densitet av gränssnittstillstånd (Dit), och portläckage. Om man på allvar vill driva fram 2-D-transistorteknik, denna klyfta måste övervinnas."

Det tillvägagångssätt som introducerats av Wang och hans kollegor möjliggör produktion av dielektrik med en ekvivalent tjocklek av 1 nm på grafen, molybdendisulfid (MoS 2 ) och volframdiselenid (WSe 2 ). Dielektriken som härrör från forskarnas tillvägagångssätt uppvisar en minskad grovhet, densitet av gränssnittstillstånd och läckage jämfört med de som produceras med mer konventionella metoder. Intressant, de presenterar också ett förbättrat uppdelningsfält.

"Andra än 2D-transistorer, en annan riktning som min forskargrupp utforskar är organisk elektronik, " tillade Wang. "Under de senaste åren, vi har utvecklat metoder för att exakt styra sammansättningen av molekyler på 2D-materialytan. För många molekyler, inklusive PTCDA, vi bevisade att vi kan kontrollera tillväxten så bra att endast ett monolager (~0,3 nm) deponeras enhetligt, med ett mycket rent gränssnitt."

Gränssnittsskiktet skapat av Wang och hans forskargrupp i deras tidigare arbete är ett av de tunnaste gränssnittsskikten som för närvarande kan uppnås. I deras nuvarande studie, de använde detta lager för att tillverka grafenradiofrekvenstransistorer som arbetar vid 60 GHz, samt MoS 2 och WSe 2 kompletterande metalloxid-halvledartransistorer med en matningsspänning på 0,8 V och en låg svängning på 60 mV dec. -1 . Till sist, de använde också sin teknik för att skapa MoS 2 transistorer med en kanallängd på 20 nm med ett på/av-förhållande på över 10 7 .

"Jag tror att vårt mest meningsfulla resultat var att vi kunde uppnå 1 nm EOT i 2D-material, " Wang sa. "Det är allmänt trott att 2-D-kanal kan minska strömförbrukningen för transistorer jämfört med bulkhalvledare. Dock, för att uppnå det, vi måste använda samma driftspänning, och transistorerna kan stängas av kraftigt (undertröskelsvängning nära 60 mV/dec). Båda kvantiteterna beror i hög grad på kvaliteten och tjockleken på grinddielektrikum. Vår studie visar verkligen potentialen hos 2D-halvledare mot lågeffektelektronik."

Wang och hans forskargrupp var de första som framgångsrikt utvecklade 2-D transistorer med en 1 nm EOT, framgångsrikt deponera dielektrikum på tre olika material. Anmärkningsvärt, EOT- och gate-läckaget de uppnådde är jämförbara med de som observeras i toppmoderna kisel-CMOS, vilket är ett viktigt steg framåt inom detta forskningsområde.

"Jag tror att det fortfarande finns mycket utrymme för förbättringar, " sa Wang. "Till exempel, Dit i 2-D-transistorer är fortfarande ~ 2 storleksordningar högre än Si CMOS. Dessutom, det skulle vara bra att ytterligare minska EOT till ~0,8nm genom att använda högre k-oxider. Till sist, kompatibiliteten för de material vi utvecklat med befintliga CMOS -processer återstår också att studera. "

© 2020 Science X Network