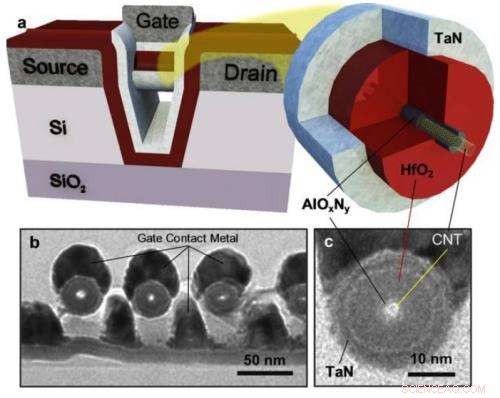

(a) Tvärsnittsdiagram av CNTFET som illustrerar hur CNT-kanalen (genomsnittsdiagram visas till höger) är upphängd över kiseldiket och kontaktas på vardera sidan av källan/dräneringen. (b) och (c) visar TEM-bilder i tvärsnitt av nanorör med en gate-all-around-geometri, som skyddar nanorören från påverkan av närliggande enheter och herrelösa laddningar. Kredit:Franklin, et al. ©2013 American Chemical Society

(Phys.org) – Under hela 70-talet, 80- och 90-tal, transistorprestanda ökade kontinuerligt enligt några enkla skalningsregler. Dessa regler postulerar att transistorstorlek och matningsspänning bör minska när effekttätheten förblir konstant, vilket resulterar i en total ökning av prestanda. Dock, fysiska begränsningar stoppade matningsspänningsskalningen i början av 2000-talet, så de enkla skalningsreglerna gäller inte längre. Nu kommer varje ökning av prestanda på bekostnad av en ökning av strömförbrukningen, så att transistorprestanda har planat ut sedan mitten av 2000-talet.

Nu i en ny studie, forskare vid IBM T.J. Watson Research Center i Yorktown Heights, New York, har utnyttjat potentialen hos kolnanorör som ett sätt att utöka skalningsreglerna och uppnå ytterligare prestandaförbättringar i transistorer. En dag, transistorer gjorda av kolnanorör kan utgöra ryggraden i många av våra elektroniska enheter, inklusive smarta telefoner och surfplattor.

Det skalningsavbrott som transistorer stötte på under det senaste decenniet berodde till stor del på de fysiska egenskaperna hos transistorerna själva, som är kiselmetall-oxid-halvledarfälteffekttransistorer (MOSFET). Under de senaste åren, forskare har undersökt möjligheten att ersätta MOSFETs med kolnanorörsfälteffekttransistorer (CNTFET). Dessa transistorer har redan visat många attraktiva egenskaper, inklusive bra prestanda vid låga spänningar med kanalkomponenter på mindre än 10 nm i längd – en skala som kisel MOSFETs inte fysiskt kan nå med bra prestanda.

"Det finns två främsta anledningar till varför CNTFET:er ger fördelar som MOSFET:er inte kan:1) CNT:erna är ultratunna kroppshalvledare (~1 nm), vilket gör att de kan integreras i aggressivt skalade enheter utan att förlora kontrollen över strömmen i kanalen; och 2) CNTFET:er kan arbeta vid låga matningsspänningar, vilket innebär att de kan ge den nivå av elektrisk ström som behövs för att driva integrerade kretsar med lägre spänning än vad MOSFET-enheter någonsin kan uppnå, " berättade medförfattaren och IBM-forskaren Aaron D. Franklin Phys.org . "I nästan ett decennium, det har skett liten eller ingen minskning av matningsspänningen för MOSFET-teknologier – CNTFET:er är ett av de bästa alternativen för att ändra den trenden."

Dock, att konkurrera med MOSFETS, CNTFET kräver fortfarande flera stora framsteg, inklusive en skalbar grind som kan anpassa sig själv till käll- och dräneringskontakterna, komplementära enheter av n- och p-typ (som skiljer sig på grund av polarisering), och kompatibilitet med trådbearbetningen som behövs för att bygga kretsar.

I deras tidning, forskarna har uppfyllt alla dessa tre krav genom att bygga en CNT-transistor med en grind som helt omger CNT-kanalen. Forskarna förklarar att denna gate-all-around (GAA) geometri är idealisk eftersom den skyddar CNT från koppling till angränsande CNT och från herrelösa laddningar som kommer för nära i så liten skala och orsakar instabilitet.

"Den största betydelsen av detta arbete är implementeringen av en grind som helt omsluter de cylindriska CNT-kanalerna, ", sa Franklin. "Eftersom nanorör bara är enstaka molekyler med ~1 nm diameter och är gjorda av ett enda skal av atomer (ihåligt på insidan), de är mycket känsliga för elektriska störningar i sin närhet. Genom att linda in varje CNT-kanal i sin egen dielektriska och metallport, de blir isolerade från sådana störningar och tar enheterna ett steg närmare en reproducerbar och pålitlig teknologi."

Den omslutande grinden är också självinriktad med käll- och avloppskontakterna utan att behöva litografi. Som en självinriktad grind, den överlappar eller överlappar inte källan/dräneringen, men passar nästan perfekt, vilket är viktigt för att säkerställa en bra väg för laddflödet. Forskarna kunde också skala ner grindens längd till 20 nm, och förutsäga att ytterligare skalning är möjlig för ännu mindre CNT-kanaler.

Grinden kan också användas för att realisera enheter av både n- och p-typ genom att använda olika dielektriska material för att ändra polariteten. Även om enheten av n-typ har bättre prestanda än enheten av p-typ, forskarna förutspår att det senare kan förbättras genom att göra tunnare spacerregioner, eftersom dessa distanser skapar en barriär för laddningstransport.

Forskarna utförde också kvantsimuleringar av CNTFET för att bekräfta deras förståelse av enhetens funktion. Simuleringsresultaten stämde väl överens med experimentresultaten, och gjorde det också möjligt för forskarna att projicera effekterna av olika variabler på enhetens prestanda, inklusive distanstjocklek och dopning. Dessa modifieringar skulle teoretiskt kunna öka påströmmen, minska frånströmmen, och leverera en undertröskelsväng mycket nära den teoretiska gränsen på 60 mv/dec, vilket innebär att transistorn kan växla mycket snabbt mellan på och av.

Går framåt, resultaten visar att arrayer av CNT kan integreras i skalbara, självjusterade transistorer av n- och p-typ med idealiska omslutande grindar. Forskarna förutspår att med ytterligare optimering, dessa CNTFET:er kan en dag fungera som lågspänning, högpresterande transistorer som har en utbredd inverkan på framtida applikationer.

"På IBM, vi har visat under de senaste åren att du kan uppnå utmärkt CNTFET-prestanda ner till under 10 nm kanallängder och nu kan göra det i en teknologiskt kompatibel wrap-gate-struktur, ", sade Franklin. "Den största utmaningen som återstår på enhetsnivå är att förbättra injektionen av bärare vid metall-CNT-kontakterna på enheterna. När kontakter skalas till de små dimensionerna som behövs för en teknik, kontaktmotståndet ökar avsevärt och måste åtgärdas. Även om detta problem inte är unikt för CNTFETs (MOSFETs av alla typer lider på liknande sätt), det är ett hinder som kräver en lösning för att få tillgång till den fulla potentialen hos en CNT-teknik.

"Utanför enhetsområdet, de två stora materialhindren är att fortsätta öka renheten och isoleringen av halvledande CNT från deras metalliska motsvarigheter och att exakt sätta ihop CNT till exakta platser på ett substrat. Båda dessa områden har sett imponerande framsteg under det senaste året, både från IBM och andra forskargrupper."

© 2013 Phys.org. Alla rättigheter förbehållna.