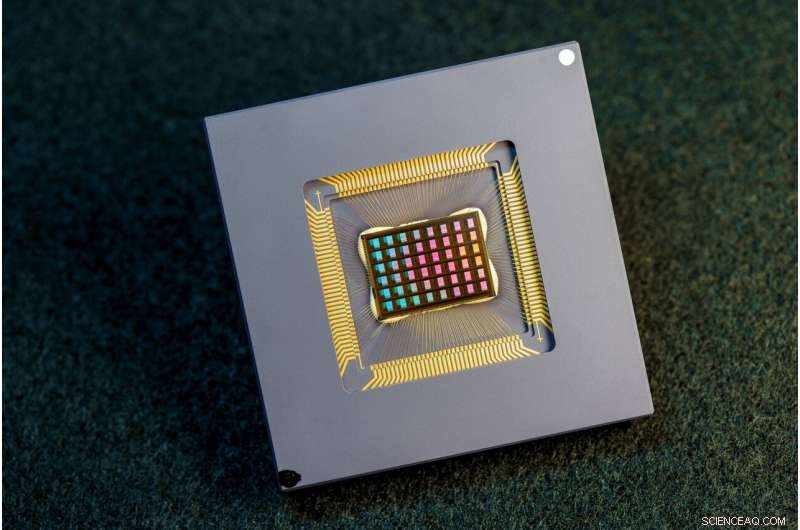

Ett team av internationella forskare designade, tillverkade och testade NeuRRAM-chippet. Kredit:David Baillot/University of California San Diego

Ett internationellt team av forskare har designat och byggt ett chip som kör beräkningar direkt i minnet och kan köra en mängd olika AI-applikationer – allt till en bråkdel av den energi som förbrukas av datorplattformar för allmän AI-beräkning.

NeuRRAM neuromorfa chip tar AI ett steg närmare att köra på ett brett utbud av edge-enheter, bortkopplade från molnet, där de kan utföra sofistikerade kognitiva uppgifter var som helst och när som helst utan att förlita sig på en nätverksanslutning till en centraliserad server. Applikationer finns i överflöd i alla hörn av världen och alla aspekter av våra liv, och sträcker sig från smarta klockor till VR-headset, smarta öronsnäckor, smarta sensorer i fabriker och rovers för rymdutforskning.

NeuRRAM-chippet är inte bara dubbelt så energieffektivt som de toppmoderna "compute-in-memory"-chipsen, en innovativ klass av hybridchips som kör beräkningar i minnet, det ger också resultat som är lika exakta som konventionella digitala chips. Konventionella AI-plattformar är mycket skrymmande och är vanligtvis begränsade till att använda stora dataservrar som arbetar i molnet.

Dessutom är NeuRRAM-chippet mycket mångsidigt och stöder många olika neurala nätverksmodeller och arkitekturer. Som ett resultat kan chippet användas för många olika applikationer, inklusive bildigenkänning och rekonstruktion samt röstigenkänning.

"Den konventionella visdomen är att den högre effektiviteten av compute-in-memory är på bekostnad av mångsidighet, men vårt NeuRRAM-chip uppnår effektivitet samtidigt som det inte offra mångsidighet", säger Weier Wan, tidningens första motsvarande författare och nyligen doktor. examen från Stanford University som arbetade på chipet vid UC San Diego, där han fick råd av Gert Cauwenberghs på institutionen för bioteknik.

Forskargruppen, som leds av bioingenjörer vid University of California San Diego, presenterar sina resultat i numret av Nature den 17 augusti. .

För närvarande är AI-datorer både energikrävande och beräkningsmässigt dyrt. De flesta AI-applikationer på edge-enheter innebär att data flyttas från enheterna till molnet, där AI bearbetar och analyserar det. Därefter flyttas resultaten tillbaka till enheten. Det beror på att de flesta edge-enheter är batteridrivna och som ett resultat bara har en begränsad mängd kraft som kan dedikeras till datoranvändning.

Genom att minska strömförbrukningen som behövs för AI-inferens vid kanten, kan detta NeuRRAM-chip leda till mer robusta, smartare och tillgängliga kantenheter och smartare tillverkning. Det kan också leda till bättre datasekretess eftersom överföring av data från enheter till molnet kommer med ökade säkerhetsrisker.

På AI-chips är att flytta data från minnet till datorenheter en stor flaskhals.

"Det motsvarar att pendla åtta timmar för en tvåtimmars arbetsdag", sa Wan.

För att lösa detta problem med dataöverföring använde forskare det som kallas resistivt slumpmässigt minne, en typ av icke-flyktigt minne som möjliggör beräkning direkt i minnet snarare än i separata datorenheter. RRAM och andra framväxande minnesteknologier som används som synapsmatriser för neuromorfisk beräkningar var banbrytande i labbet av Philip Wong, Wans rådgivare på Stanford och en huvudsaklig bidragsgivare till detta arbete. Beräkning med RRAM-chips är inte nödvändigtvis nytt, men generellt leder det till en minskning av noggrannheten i de beräkningar som utförs på chippet och en brist på flexibilitet i chipets arkitektur.

"Compute-in-memory har varit vanligt förekommande inom neuromorfisk teknik sedan det introducerades för mer än 30 år sedan," sa Cauwenberghs. "Vad som är nytt med NeuRRAM är att den extrema effektiviteten nu går ihop med stor flexibilitet för olika AI-tillämpningar med nästan ingen förlust i noggrannhet jämfört med vanliga digitala generella datorplattformar."

En noggrant utformad metodik var nyckeln till arbetet med flera nivåer av "samoptimering" över abstraktionsskikten av hårdvara och mjukvara, från designen av chipet till dess konfiguration för att köra olika AI-uppgifter. Dessutom såg teamet till att ta hänsyn till olika begränsningar som sträcker sig från minnesenhetsfysik till kretsar och nätverksarkitektur.

"Detta chip ger oss nu en plattform för att ta itu med dessa problem över hela stacken från enheter och kretsar till algoritmer", säger Siddharth Joshi, biträdande professor i datavetenskap och teknik vid University of Notre Dame, som började arbeta med projektet som en Ph.D. student och postdoktor i Cauwenberghs labb vid UC San Diego.

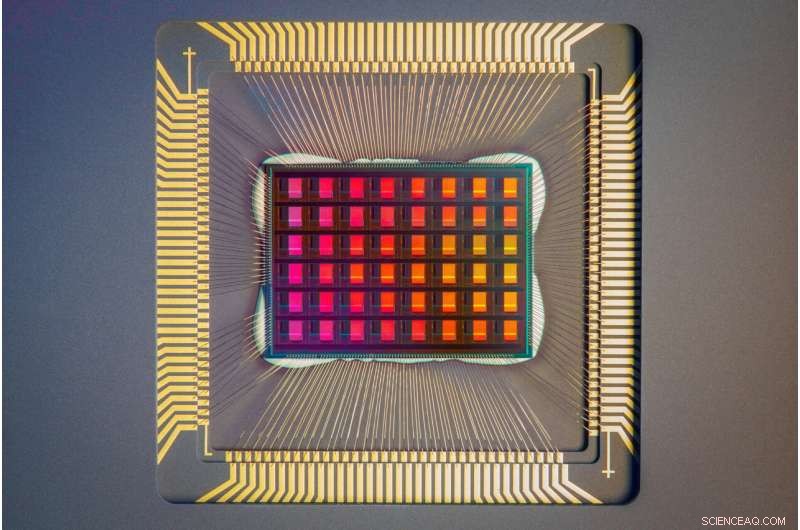

En närbild av NeuRRAM-chippet. Kredit:David Baillot/University of California San Diego

Chipprestanda

Forskare mätte chipets energieffektivitet med ett mått som kallas energifördröjningsprodukt eller EDP. EDP kombinerar både mängden energi som förbrukas för varje operation och antalet gånger det tar att slutföra operationen. Genom denna åtgärd uppnår NeuRRAM-chippet 1,6 till 2,3 gånger lägre EDP (lägre är bättre) och 7 till 13 gånger högre beräkningstäthet än toppmoderna chips.

Forskare körde olika AI-uppgifter på chipet. Den uppnådde 99 % noggrannhet på en handskriven siffrorigenkänningsuppgift; 85,7 % på en bildklassificeringsuppgift; och 84,7 % på en Google-uppgift för talkommandoigenkänning. Dessutom uppnådde chippet också en 70 % minskning av bildrekonstruktionsfel på en bildåterställningsuppgift. Dessa resultat är jämförbara med befintliga digitala chips som utför beräkningar med samma bitprecision, men med drastiska besparingar i energi.

Researchers point out that one key contribution of the paper is that all the results featured are obtained directly on the hardware. In many previous works of compute-in-memory chips, AI benchmark results were often obtained partially by software simulation.

Next steps include improving architectures and circuits and scaling the design to more advanced technology nodes. Researchers also plan to tackle other applications, such as spiking neural networks.

"We can do better at the device level, improve circuit design to implement additional features and address diverse applications with our dynamic NeuRRAM platform," said Rajkumar Kubendran, an assistant professor for the University of Pittsburgh, who started work on the project while a Ph.D. student in Cauwenberghs' research group at UC San Diego.

In addition, Wan is a founding member of a startup that works on productizing the compute-in-memory technology. "As a researcher and an engineer, my ambition is to bring research innovations from labs into practical use," Wan said.

New architecture

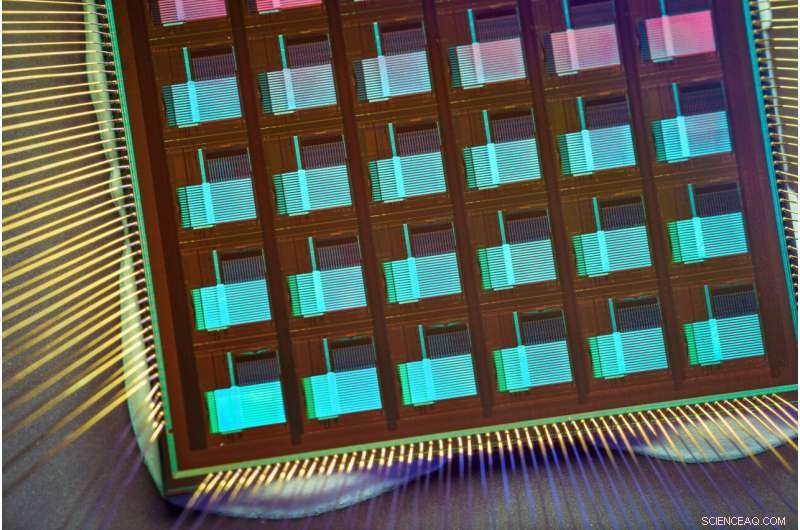

The key to NeuRRAM's energy efficiency is an innovative method to sense output in memory. Conventional approaches use voltage as input and measure current as the result. But this leads to the need for more complex and more power hungry circuits. In NeuRRAM, the team engineered a neuron circuit that senses voltage and performs analog-to-digital conversion in an energy efficient manner. This voltage-mode sensing can activate all the rows and all the columns of an RRAM array in a single computing cycle, allowing higher parallelism.

In the NeuRRAM architecture, CMOS neuron circuits are physically interleaved with RRAM weights. It differs from conventional designs where CMOS circuits are typically on the peripheral of RRAM weights.The neuron's connections with the RRAM array can be configured to serve as either input or output of the neuron. This allows neural network inference in various data flow directions without incurring overheads in area or power consumption. This in turn makes the architecture easier to reconfigure.

To make sure that accuracy of the AI computations can be preserved across various neural network architectures, researchers developed a set of hardware algorithm co-optimization techniques. The techniques were verified on various neural networks including convolutional neural networks, long short-term memory, and restricted Boltzmann machines.

As a neuromorphic AI chip, NeuroRRAM performs parallel distributed processing across 48 neurosynaptic cores. To simultaneously achieve high versatility and high efficiency, NeuRRAM supports data-parallelism by mapping a layer in the neural network model onto multiple cores for parallel inference on multiple data. Also, NeuRRAM offers model-parallelism by mapping different layers of a model onto different cores and performing inference in a pipelined fashion.

The NeuRRAM chip uses an innovative architecture that has been co-optimized across the stack. Credit:David Baillot/University of California San Diego

An international research team

The work is the result of an international team of researchers.

The UC San Diego team designed the CMOS circuits that implement the neural functions interfacing with the RRAM arrays to support the synaptic functions in the chip's architecture, for high efficiency and versatility. Wan, working closely with the entire team, implemented the design; characterized the chip; trained the AI models; and executed the experiments. Wan also developed a software toolchain that maps AI applications onto the chip.

The RRAM synapse array and its operating conditions were extensively characterized and optimized at Stanford University.

The RRAM array was fabricated and integrated onto CMOS at Tsinghua University.

The Team at Notre Dame contributed to both the design and architecture of the chip and the subsequent machine learning model design and training. + Utforska vidare